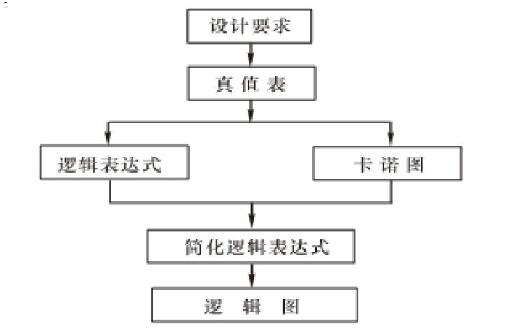

1.使用中、小規(guī)模集成電路來設(shè)計(jì)組合電路是最常見的邏輯電路設(shè)計(jì)方法。設(shè)計(jì)組合電路的一般步驟如圖所示。

2.組合邏輯電路的設(shè)計(jì)

步驟:①根據(jù)對邏輯功能要求,列真值表

②由真值表寫出邏輯表達(dá)式

③根據(jù)要求化簡和變換邏輯函數(shù)表達(dá)式

④根據(jù)要求畫出邏輯圖

⑤芯片選擇,接成實(shí)物

⑥分析并比較設(shè)計(jì)的優(yōu)劣

設(shè)計(jì)目標(biāo):電路簡單,所用器件最少,可靠性好等

二、三人表決電路設(shè)計(jì)要求:設(shè)計(jì)一個(gè)三人表決電路,結(jié)果按“少數(shù)服從多數(shù)”的原則決定。

方法:

(1):只用74LS00,74LS20實(shí)現(xiàn)。

(SSI設(shè)計(jì))

(2):用74LS138和74LS20實(shí)現(xiàn)。

(MSI設(shè)計(jì))

(3):用74LS151或LS153實(shí)現(xiàn)。

(MSI設(shè)計(jì))

方法一:用SSI設(shè)計(jì)(用74LS00,74LS20)實(shí)現(xiàn)三人表決電路

分析:

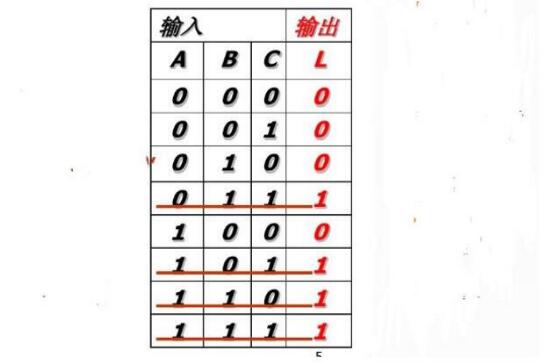

①設(shè)A、B、C:三人的意見。

同意為邏輯“1”;不同意為邏輯“0”

L:表決結(jié)果。

事件通過為邏輯“1”;沒通過為邏輯“0”

列出真值表如右表所示。

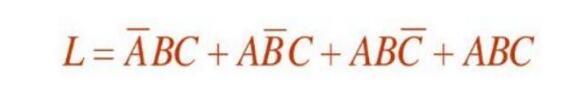

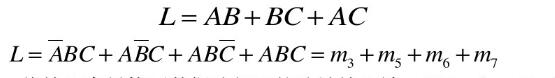

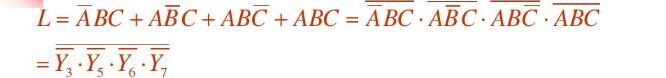

②由真值表寫出邏輯表達(dá)式:

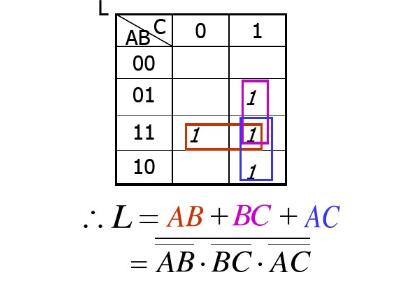

③用卡諾圖進(jìn)行化簡。

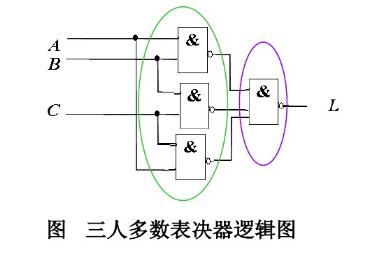

④畫出邏輯圖。

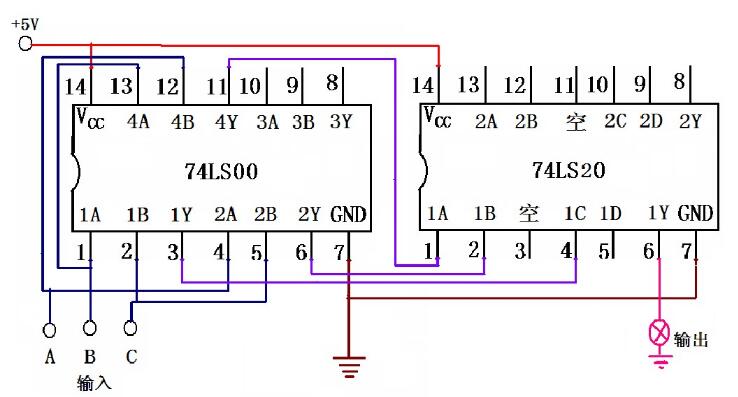

⑤選擇芯片并連接。

用74LS00和74LS20實(shí)物接線如下:

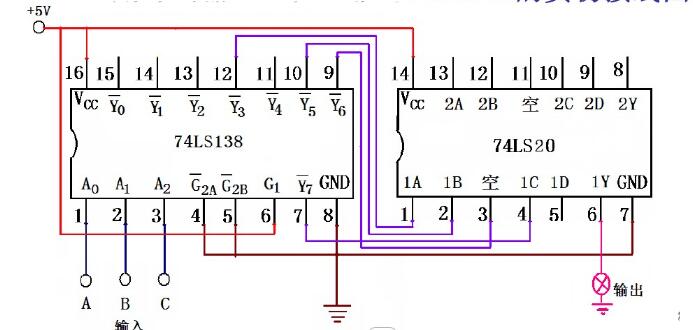

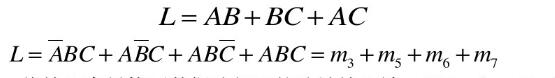

方法二:用譯碼器138和與非門74LS20設(shè)計(jì)實(shí)現(xiàn)三人表決電路

用譯碼器138和與非門74LS20的實(shí)物接線圖

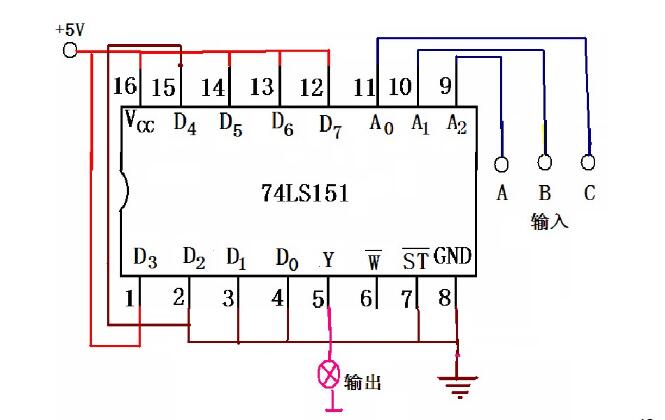

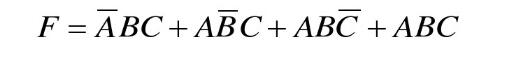

方法三:用8選1數(shù)據(jù)選擇器74LS151實(shí)現(xiàn)三人表決電路

將輸入變量接至數(shù)據(jù)選擇器的地址輸入端,即A=A2,B=A1,C=A0。輸出變量接至數(shù)據(jù)選擇器的輸出端,即L=Y。將邏輯函數(shù)L的最小項(xiàng)表達(dá)式與74151的功能表相比較,

用數(shù)據(jù)選擇器74LS151實(shí)現(xiàn)接線圖

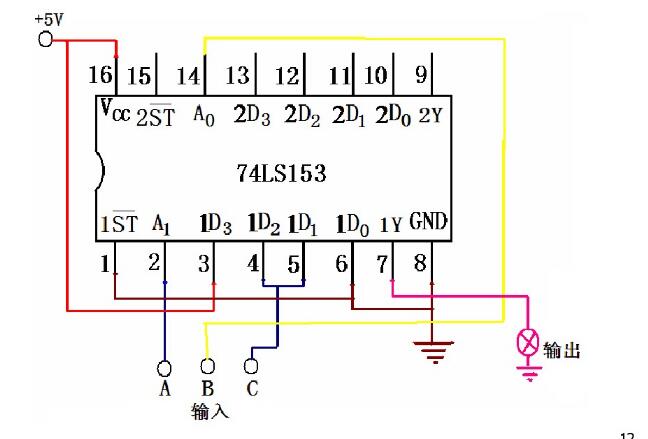

方法四:用4選1數(shù)據(jù)選擇器74LS153實(shí)現(xiàn)三人表決電路

該邏輯函數(shù)含有三個(gè)邏輯變量,可選其中的兩個(gè)(A,B)作為數(shù)據(jù)選擇器的地址輸入變量,一個(gè)(C)作為數(shù)據(jù)輸入變量。

用數(shù)據(jù)選擇器74LS153實(shí)現(xiàn)接線圖

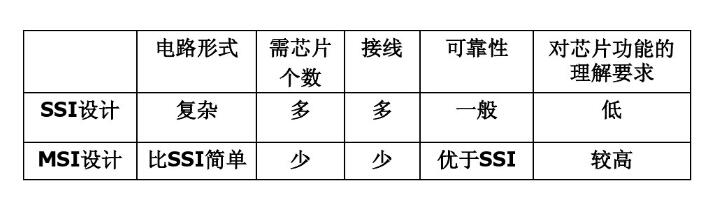

比較:

結(jié)論:MSI設(shè)計(jì)優(yōu)于SSI設(shè)計(jì)的。

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底