阻抗控制部分包括兩部分內容:基本概念及阻抗匹配。本篇主要介紹阻抗控制相關的一些基本概念。

1、阻抗

在具有電阻、電感和電容的電路里,對交流電所起的阻礙作用叫做阻抗。阻抗常用Z表示。阻抗由電阻、感抗和容抗三者組成,但不是三者簡單相加。阻抗的單位是歐。在直流電中,物體對電流阻礙的作用叫做電阻,世界上所有的物質都有電阻,只是電阻值的大小差異而已。

在交流電的領域中則除了電阻會阻礙電流以外,電容及電感也會阻礙電流的流動,這種作用就稱之為電抗,意即抵抗電流的作用。電容及電感的電抗分別稱作容抗及感抗。它們的計量單位與電阻一樣是歐姆,而其值的大小則和交流電的頻率有關系,頻率愈高則容抗愈小感抗愈大,頻率愈低則容抗愈大而感抗愈小。此外容抗和感抗還有相位角度的問題,具有向量上的關系式,因此阻抗是電阻與電抗在向量上的和。對于一個具體電路,阻抗不是不變的,而是隨著頻率變化而變化。在電阻、電感和電容串聯電路中,電路的阻抗一般來說比電阻大,也就是阻抗減小到最小值。在電感和電容并聯電路中,諧振的時候阻抗增加到最大值,這和串聯電路相反。

阻抗即電阻與電抗的總和,用數學形式表示為:

Z=R+jX

Z即阻抗,單位為歐姆Ω

R為電阻,單位為歐姆Ω

X為電抗,單位為歐姆Ω

當X>0時,稱為感性電抗

當X=0時,電抗為0

當X<0時,稱為容性電抗

對電阻為0的理想純感抗或容抗元件,阻抗強度就是電抗的大小。一般電路的總電抗等于:

X=XL−Xc

其中XL為電路的感抗,Xc為電路的容抗。

感抗(XL)一般是因為電路中存在電感電路(如線圈等),由此產生的變化的電磁場,會產生相應的阻礙電流流動的電動力。電流變化越大,即電路頻率越大,感抗越大;當頻率變為0,即成為直流電時,感抗也變為0。感抗會引起電流與電壓之間的相位差。感抗可由下面公式計算而來:

XL=ωL=2×π×f×L

XL就是感抗,單位為歐姆Ω

ω是角頻率,單位為弧度/每秒rad/s

f是頻率,單位為赫茲Hz

容抗(Xc)的概念反映了交流電可以通過電容這一特性,交流電頻率越高,容抗越小,即電容的阻礙作用越小。容抗同樣會引起電流與電容兩端電壓的相位差。容抗可由下面公式計算而來:

Xc=1/(ω×C)=1/(2×π×f×C)

Xc是容抗,單位為歐姆Ω

ω是角頻率,單位為弧度/秒rad/s

f是頻率,單位為赫茲Hz

C是電容,單位為法拉F

2、輸入阻抗

輸入阻抗是指一個電路輸入端的等效阻抗。在輸入端上加上一個電壓源U,測量輸入端的電流I,則輸入阻抗Rin=U/I。

輸入阻抗跟一個普通的電抗元件沒什么兩樣,它反映了對電流阻礙作用的大小。

對于電壓驅動的電路,輸入阻抗越大,表明放大器從信號源取的電流越小,放大器輸入端得到的信號電壓也越大,即信號源電壓衰減的少,對電壓源的負載就越輕,因而就越容易驅動,也不會對信號源有影響。理論基礎:Us=(Rs+Ri)×I。Rs為信號源內阻,Ri為放大器輸入電阻。因此作為測量信號電壓的示波器、電壓表等儀器的放大電路應當具有較大的輸入電阻。對于一般的放大電路來說,輸入電阻當然是越大越好。如果想從信號源取得較大的電流,則應該使放大器具有較小的輸入電阻。

而對于電流驅動型的電路,輸入阻抗越小,則對電流源的負載就越輕。如果是用電壓源來驅動的,則輸入阻抗越大越好;如果是用電流源來驅動的,則阻抗越小越好(只適合于低頻電路,在高頻電路中,還要考慮阻抗匹配問題)。另外如果要獲取最大輸出功率時,也要考慮阻抗匹配問題。

3、輸出阻抗

無論信號源或放大器還有電源,都有輸出阻抗的問題。輸出阻抗就是一個信號源的內阻。本來,對于一個理想的電壓源(包括電源),內阻應該為0,或理想電流源的阻抗應當為無窮大。輸出阻抗在電路設計時最需要特別注意。

但現實中的電壓源,則不能做到這一點。我們常用一個理想電壓源串聯一個電阻r的方式來等效一個實際的電壓源。這個跟理想電壓源串聯的電阻r,就是(信號源/放大器輸出/電源)的內阻了。當這個電壓源給負載供電時,就會有電流I從這個負載上流過,并在這個電阻上產生I×r的電壓降。這將導致電源輸出電壓的下降,從而限制了最大輸出功率。同樣的,一個理想的電流源,輸出阻抗應該是無窮大,但實際的電路是不可能的。

輸出電阻用來衡量放大器在不同負載條件下維持輸出信號電壓(或電流)恒定能力的強弱,稱為其帶負載能力。當放大器將放大了的信號輸出給負載電阻RL時,對負載RL來說,放大器可以等效為具有內阻Ro的信號源,由這個信號源向RL提供輸出信號電壓和輸出信號電流。Ro稱為放大器的輸出電阻,它是從放大器輸出端向放大器本身看入的交流等效電阻。如果輸出電阻Ro很小,滿足Ro<<RL條件,則當RL在較大范圍內變化時,就可基本維持輸出信號電壓的恒定。反之,如果輸出電阻Ro很大,滿足Ro>>RL條件,則當RL在較大范圍內變化時,就可維持輸出信號電流的恒定。如手機電池,它的內阻可以等效看作輸出電阻,用了幾年后,內阻高了,也就要報廢了,因為帶不動外面的東西。

- CMOS電路的輸出阻抗一般為17歐姆or 10歐姆(輸出高電平和輸出低電平不一樣!!!輸出高電平時輸出阻抗為RPMOS,輸出低電平時輸出阻抗為RNMOS,由于RPMOS大于RNMOS,這是由MOS管的工藝決定的)。

- TTL電路輸出電阻大概為13歐姆左右。

4、奇模/偶模、差分/共模、奇模阻抗/共模阻抗、差分阻抗/共模阻抗

針對上述幾個基本概念解釋定義如下:

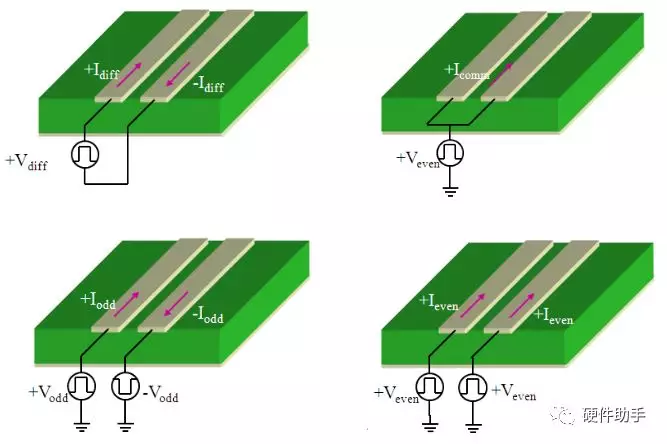

- 奇模和偶模是指差分對的特殊的固有模態。當差分線上有相反的驅動電壓時的模態稱為奇模;當差分線上有相同的驅動電壓時的模態稱為偶模。

- 差分和共模是指加在差分對上的特殊信號。任意信號之間的差分分量是指兩信號線之間的電壓差,共模分量是指兩信號線之間電壓的平均值。對于差分對而言,差分信號以奇模方式傳播,以奇模方式傳播的電壓分量Vodd就是信號的差分分量;共模信號以偶模方式傳播,以偶模方式傳播的電壓分量Veven就是信號的共模分量。

- 奇模(偶模)阻抗是指當差分對被驅動成奇模(偶模)模態時的阻抗。奇模電壓分量和偶模電壓分量在傳輸線中傳播的過程是完全能獨立的,沒有相互作用,兩個信號分量在每條信號走線及其返回路徑之間會看到不同的阻抗,即奇模阻抗和偶模阻抗。

- 差分阻抗是指差分信號沿差分對傳播時受到的阻抗,共模阻抗是指共模信號沿差分對傳播時受到的阻抗。

奇模和偶模是相對于地來說的,以地作為參考面。而差分線是相對于2根線之間的關系來說的。

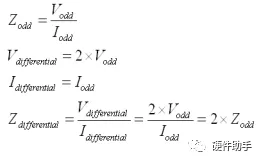

對于差分信號來說,差分阻抗是奇模阻抗的2倍。

對于共模信號來說,共模阻抗是偶模阻抗的一半。

5、特征阻抗(Characteristic Impedance)

特征阻抗是指信號沿傳輸線傳播時,信號看到的瞬時阻抗的值。特征阻抗與PCB導線所在的板層、PCB所用的材質(介電常數)、走線寬度、導線與平面的距離等因素有關,與走線長度無關。特征阻抗可以用Polar Si9000軟件計算。高速PCB布線中,一般把數字信號的走線阻抗設計為50歐姆,這是個大約的數字。一般規定同軸電纜基帶50歐姆,頻帶75歐姆,雙絞線(差分)為100歐姆。

下表是一些常見的單端/差分信號特征阻抗值。

在高速信號中,我們經常把差分阻抗控制在100歐姆,單端控制在50歐姆,為何不是其他的阻值呢?有人說,是因為芯片匹配要求的。那么芯片為何要把匹配做成50歐姆(100歐姆)呢?

因為,特征阻抗為30歐姆的時候,頻率響應特性很好,但是傳輸損耗比較大。而75歐姆的特性阻抗的情況下,傳輸損耗比較小,但是頻率特性比較差。于是最終折中到50歐姆上。

這就可以理解2M同軸線、155M同軸線都是75歐姆,而不是50歐姆的原因,是為了減少損耗,提高傳輸距離。

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底