數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關。

而時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決于當時的輸入信號,而且還取決于電路原來的狀態,或者說,還與以前的輸入有關。

組合邏輯電路的特點

1、邏輯功能特點

組合邏輯電路任一時刻的輸出狀態,只決定于該時刻輸入信號的狀態,而與輸入信號作用前電路原來的狀態無關。

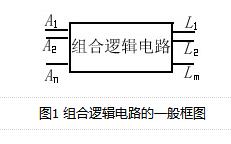

圖1是組合邏輯電路的一般框圖,它可用如下的邏輯函數來描述,即

Li=f(A1,A2,…,An) (i=1,2,…,m)式中A1,A2,…,An為輸入變量。

2、電路結構特點

組合邏輯電路全部由門電路組成,電路中不含記憶單元,由輸出到輸入沒有任何反饋線。

3、組合邏輯電路的特點

1)邏輯門電路組成,電路中不包含任何記憶元件;

2)信號是單向傳輸的,電路中不存在任何反饋回路。

組合邏輯電路的原理

組合邏輯電路是指在任何時刻,輸出狀態只決定于同一時刻各輸入狀態的組合,而與電路以前狀態無關,而與其他時間的狀態無關。其邏輯函數如下:

Li=f(A1,A2,A3……An) (i=1,2,3…m)

其中,A1~An為輸入變量,Li為輸出變量。

組合邏輯電路的特點歸納如下:

① 輸入、輸出之間沒有返饋延遲通道;

② 電路中無記憶單元。

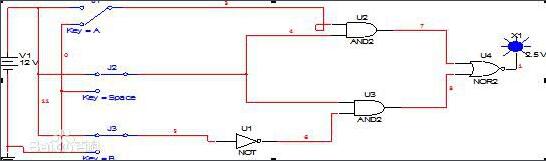

對于第一個邏輯表達公式或邏輯電路,其真值表可以是惟一的,但其對應的邏輯電路或邏輯表達式可能有多種實現形式,所以,一個特定的邏輯問題,其對應的真值表是惟一的,但實現它的邏輯電路是多種多樣的。在實際設計工作中,如果由于某些原因無法獲得某些門電路,可以通過變換邏輯表達式變電路,從而能使用其他器件來代替該器件。同時,為了使邏輯電路的設計更簡潔,通過各方法對邏輯表達式進行化簡是必要的。組合電路可用一組邏輯表達式來描述。設計組合電路直就是實現邏輯表達式。要求在滿足邏輯功能和技術要求基礎上,力求使電路簡單、經濟、可靠、實現組合邏輯函數的途徑是多種多樣的,可采用基本門電路,也可采用中、大規模集成電路。其一般設計步驟為:

① 分析設計要求,列真值表;

② 進行邏輯和必要變換。得出所需要的最簡邏輯表達式;

③ 畫邏輯圖。

組合邏輯電路的運算單元

在數字系統中算術運算都是利用加法進行的,因此加法器是數字系統中最基本的運算單元。由于二進制運算可以用邏輯運算來表示,因此可以用邏輯設計的方法來設計運算電路。加法在數字系統中分為全加和半加,所以加法器也分為全加器和半加器。

1、半加器設計

半加器不考慮低位向本位的進位,因此它有兩個輸入端和兩個輸出端。

設加數(輸入端)為A、B ;和為S ;向高位的進位為Ci+1

函數的邏輯表達式為: S=AB+AB ; Ci+1=AB+1

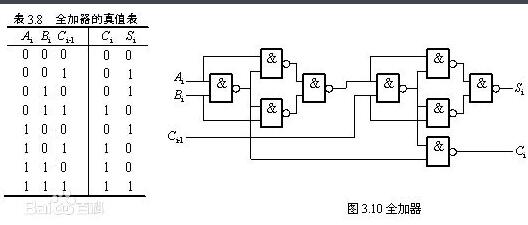

2、全加器設計

由于全加器考慮低位向高位的進位,所以它有三個輸入端和兩個輸出端。設輸入變量為(加數)A、B、 Ci-1,輸出變量為 S、 Ci+1

函數的邏輯表達式為:S=ABCi-1+ABCi-1+ABCi-1+ABCi-1=ABCi-1

Ci+1=ABCi-1+ABCi-1+ABCi-1+ABCi-1 =(AB)Ci-1+AB

3、全加器應用

因為加法器是數字系統中最基本的邏輯器件,所以它的應用很廣。它可用于二進制的減法運算、乘法運算,BCD碼的加、減法,碼組變換,數碼比較等。

常用的組合邏輯電路

1、法器

實現1位二進制數之間加法運算的電路稱為1位加法器。根據加數的不同,1位加法器又分為半加器和全加器兩種電路類型。如果不考慮來自低位的進位而是只將兩個1位二進制數相加,即只有加數和被加數相加,這種加法運算稱為半加運算。實現半加運算的電路叫做半加器。串行進位加法器的優點是電路比較簡單,缺點是速度比較慢。

2、編碼器

在數字系統中,所謂編碼,就是將字母、數字、符號等信息編成一組二進制代碼的過程。編碼器是數字電路中常用的集成電路之一。最常見的計算機鍵盤中就含有編碼器器件,當按下鍵盤上的按鍵時,編碼器將按鍵信息轉換成二進制代碼,并將這組二進制代碼送到計算機進行處理。目前經常使用的編碼器有普通編碼器和優先編碼器兩類。

3、譯碼器

譯碼是編碼的反過程。編碼是將信號轉換成二進制代碼,譯碼則是將二進制代碼轉換成特定的信號。將輸入的二進制代碼轉換成特定的高(低)電平信號輸出的邏輯電路稱為譯碼器。

4、據選擇器

數據選擇器的功能是根據地址選擇碼從多路輸入數據中選擇一路送到輸出。

當輸入信號經過不同的路徑傳輸到同一個門電路時,由于信號所經過的門電路的傳輸延時不同,或者所經過的門電路的級數不同,導致信號到達匯合點門電路的時間不同,從而可能引起該門電路的輸出波形出現尖峰脈沖(干擾信號),這一現象稱為組合邏輯電路中的競爭-冒險現象。

產生競爭-冒險的原因是由于一個門的兩個互補的輸入信號分別經過兩條不同的路徑傳輸,由于延遲時間不同,而到達的時間不同引起的。消除競爭-冒險的方法主要有引入封鎖脈沖、引入選通脈沖、接濾波電容或修改邏輯設計等。

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底