數值比較器就是對兩個數A、B進行比較,以便判斷其大小的邏輯電路。

一、1位數值比較器

圖4.21是1位數值比較器的邏輯圖。它有兩個輸入端,分別輸入數值A和數值B。兩個數值進行比較時有三種結果:A>B、A=B以及A<B。所以它有三個輸出端。

圖4.21 1位數值比較器

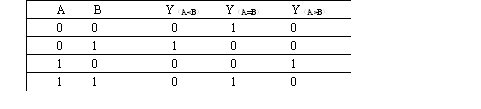

根據邏輯表達式4.6可以列出真值表如表4.12所示。

表4.12 1位數值比較器真值表

由表4.12可以看出,當A<B (A=0,B=1) 時只有Y(A<B)=1,其余輸出端為“0”;當A=B(A=0,B=0和A=1,B=1)時Y(A=B)=1;當A>B (A=1,B=0) 時Y(A>B)=1。該電路可以根據輸出端的邏輯狀態,判斷出輸入的兩個1位二進制數A、B的大小。完成的是1位數值比較的邏輯功能,所以它是1位數值比較器。在實際應用中往往需要比較兩個多位二進制數,就需要把上面的1位數值比較器合理的連接起來使用,組成多位數值比較器

當兩個多位二進制數需要比較時,應該從高位到低位,逐位進行比較,而且只有當高位相等時,才有必要比較相鄰的低一位,一直到最低一位。例如兩個4位二進制數,A=A3A2A1A0、B=B3B2B1B0進行比較時,如果A3>B3說明A>B;如果A3<B3說明A<B;只有當A3=B3時,需要比較A2和B2,按此方法從高位到低位依次進行比較,即可以得出最后的比較結果。按照此思路設計出的中規模數值比較器有多種。例如74LS521、74LS686 為8位數值比較器、CC4585為4位數值比較器等等。圖4.22(a)為74LS686管腳排列圖,圖4.22(b)為CC4585管腳排列圖。74LS686功能表如表4.13所示。

圖4.22 數值比較器管腳排列圖

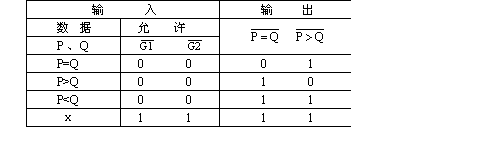

表4.13 74LS686功能表

174LS686可以對兩個8位數進行逐位比較。由表4.13可以看出,當P=Q輸出端為低電平時表示兩個8位數完全相等;當P>Q輸出端為低電平時表示P8位數大于Q8位數;當兩個輸出端都輸出高電平(即不相等,也不大于)時表示P8位數小于Q8位數。

G1和G2 為控制端,低電平有效。即G1 = G2=0時比較器正常工作, G1 = G2 =1時比較器不工作。

圖4.22(b)中的CC4585為4位數值比較器。為了擴展邏輯功能,設計了低位比較輸入端。內部結構要求,只比較兩個4位數時,要求“輸入A<B”=0、“輸入A=B”=1、“輸入A>B”=1。

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底