常用時序邏輯電路有計數(shù)器和寄存器兩種。寄存器分為數(shù)據(jù)寄存器和移位寄存器。計數(shù)器種類較多,有同步計數(shù)器、異步計數(shù)器;有二進制計數(shù)器、十進制計數(shù)器、任意進制計數(shù)器;二進制計數(shù)器又有加法計數(shù)器、減法計數(shù)器等。

(1)寄存器

數(shù)字電路中用來存放數(shù)碼或指令的部件稱為寄存器。寄存器具有以下邏輯功能:可在時鐘脈沖作用下將數(shù)碼或指令存入寄存器(稱為寫入),或從寄存器中將數(shù)碼或指令取出(稱為讀出)。由于一個觸發(fā)器只能寄存1位二進制數(shù),要存多位數(shù)時,就得用多個觸發(fā)器。常用的有4位、8位、16位等。

寄存器存放和取出數(shù)碼的方式有并行和串行兩種。并行方式就是數(shù)碼各位同時從各對應位輸入端輸入到寄存器中,或同時出現(xiàn)在輸出端;串行方式就是數(shù)碼逐位從一個輸入端輸入到寄存器中,或由一個輸出端輸出。

寄存器根據(jù)功能的不同可分為數(shù)碼寄存器和移位寄存器兩種。

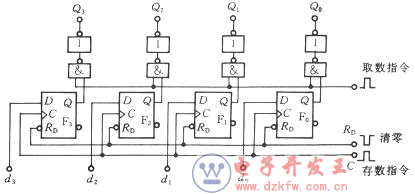

(a) 數(shù)碼寄存器:這種寄存器只有寄存數(shù)碼和清除數(shù)碼的功能。圖1所示是由D觸發(fā)器組成的4位數(shù)碼寄存器。該數(shù)碼寄存器的工作方式為并行輸入、并行輸出。

圖1 4位數(shù)碼寄存器

(b)移位寄存器:移位寄存器不僅能存放數(shù)碼而且有移位功能。根據(jù)數(shù)碼在寄存器內(nèi)移動的方向又可分為左移移位寄存器和右移移位寄存器兩種。

在移位寄存器中,數(shù)碼的存入或取出也有并行和串行兩種方式。

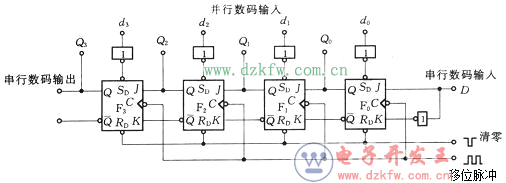

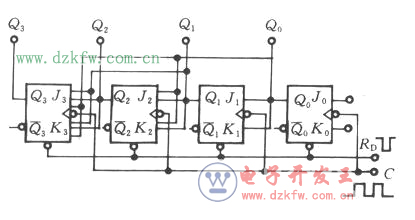

圖2所示是由J—K觸發(fā)器組成的4位左移移位寄存器。F0接成D觸發(fā)器,數(shù)碼由D端串行輸入;也可由d0~d3作并行輸入。從4個觸發(fā)器的Q端得到并行的數(shù)碼輸出。也可從Q3端逐位串行輸出。

圖2 4位左移移位寄存器

(2)計數(shù)器

因為計數(shù)器是最常用而又典型的時序邏輯電路,其分析方法即為一般時序邏輯電路的分析方法。常用計數(shù)器有多種類型,重點掌握以下幾種。

①二進制計數(shù)器:二進制計數(shù)器能按二進制的規(guī)律累計脈沖的數(shù)目,也是構成其它進制計數(shù)器的基礎。一個觸發(fā)器可以表示l位二進制數(shù),表示n位二進制數(shù)就得用n個觸發(fā)器。

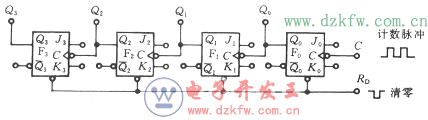

(a)異步二進制加法計數(shù)器:圖3所示邏輯電路是由4個J—K觸發(fā)器組成的4位異步二進制加法計數(shù)器。圖中各觸發(fā)器輸入端均為“1”(懸空)即計數(shù)狀態(tài)。只要有時鐘脈沖就會翻轉(zhuǎn),但前級觸發(fā)器的輸出作為后級觸發(fā)器的時鐘脈沖,只有在前級觸發(fā)器翻轉(zhuǎn)后,后級觸發(fā)器才能翻轉(zhuǎn),故為異步計數(shù)器。其狀態(tài)真值表見圖4。

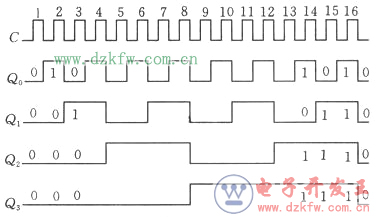

可見,在第16個時鐘脈沖到來后,計數(shù)器循環(huán)一周回到原態(tài),因此也稱為十六進制計數(shù)器。其波形圖如圖5所示,由圖可知,各觸發(fā)器輸出端Q0,Q1,Q2,Q3的脈沖頻率分別為時鐘脈沖的1/2,l/4,l/8,1/16,也稱分頻器。

圖3 4位異步二進制加法計數(shù)器

圖4異步計數(shù)器狀態(tài)真值表

圖5 十六進制計數(shù)器波形圖

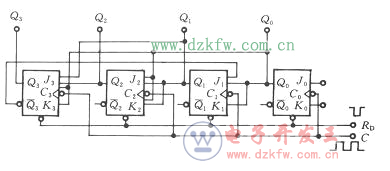

(b)同步二進制加法計數(shù)器:異步二進制計數(shù)器線路簡單,工作速度較慢。同步計數(shù)器工作速度較快,電路較復雜。圖6所示為同步4位二進制加法計數(shù)器的邏輯電路圖。從圖中可以看出計數(shù)脈沖同時供給各觸發(fā)器,它們的狀態(tài)變換和計數(shù)脈沖同步。圖中每個觸發(fā)器有多個J端和K端,各J端或各K端之間都是“與”邏輯關系。

各觸發(fā)器輸入端的邏輯表達式(驅(qū)動方程)為

J0=K0=1

J1=K1=Q0

J2=K2=Q1Q0

J3=K3= Q2Q1Q0

該計數(shù)器的狀態(tài)表和波形圖與異步4位二進制加法計數(shù)器相同。分析可知,n位二進制加法計數(shù)器能計的最大十進制數(shù)為2n-1。

圖6 同步4位二進制加法計數(shù)器的邏輯電路圖

②十進制計數(shù)器:從4位二進制數(shù)碼的16種狀態(tài)中任取10種狀態(tài),來表示1位十進制數(shù),可有多種組合,也稱編碼。常用的編碼形式是8421加權碼,相應的計數(shù)器稱8421十進制計數(shù)器。圖7所為同步十進制加法計數(shù)器。

圖7 同步十進制加法計數(shù)器

③集成計數(shù)器:將多個觸發(fā)器構成的計數(shù)器做在一塊中規(guī)模芯片上構成集成計數(shù)器,用它可構成所需模數(shù)的各種計數(shù)器。

④用中規(guī)模集成計數(shù)器組成任意進制計數(shù)器,通常有兩種方法:

(a)反饋復位法(或稱反饋“清0”法):它是利用中規(guī)模組件進行正常計數(shù),當計數(shù)器達到N進制進位要求時,形成復位脈沖,并用此脈沖反饋到組件的異步復位(/![]() )端,使計數(shù)器復位(“清0”),實現(xiàn)N進制計數(shù)功能。

)端,使計數(shù)器復位(“清0”),實現(xiàn)N進制計數(shù)功能。

(b)反饋置數(shù)法(或稱反饋預置法):根據(jù)74LSl6l等通用計數(shù)器的功能,可將任意狀態(tài)譯碼后反饋到置數(shù)命令端(![]() ),并在下一個脈沖時給計數(shù)器并行輸入0000~1111之間的任意一個狀態(tài),從而實現(xiàn)任意計數(shù)方法的N進制計數(shù)器。例如當計數(shù)器計到1001時發(fā)出反饋信號給

),并在下一個脈沖時給計數(shù)器并行輸入0000~1111之間的任意一個狀態(tài),從而實現(xiàn)任意計數(shù)方法的N進制計數(shù)器。例如當計數(shù)器計到1001時發(fā)出反饋信號給![]() ,下一個脈沖將計數(shù)器置成0100,于是計數(shù)器便成為六進制計數(shù)器,其狀態(tài)由0100到1001循環(huán)變化。這種方法稱反饋預置法。

,下一個脈沖將計數(shù)器置成0100,于是計數(shù)器便成為六進制計數(shù)器,其狀態(tài)由0100到1001循環(huán)變化。這種方法稱反饋預置法。

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底