”ө(shЁҙ)ЧЦлҠВ··ЦһйҪMәПЯүЭӢлҠВ·әН•r(shЁӘ)РтЯүЭӢлҠВ·ғЙоҗ(lЁЁi)Ј¬ҪMәПЯүЭӢлҠВ·өДМШьc(diЁЈn)КЗЭ”іцРЕМ–(hЁӨo)Ц»КЗФ“•r(shЁӘ)өДЭ”ИлРЕМ–(hЁӨo)өДәҜ”ө(shЁҙ)Ј¬Еc„e•r(shЁӘ)ҝМөДЭ”Ил о‘B(tЁӨi)ҹo(wЁІ)кP(guЁЎn)Ј¬ЛьКЗҹo(wЁІ)Уӣ‘ӣ№ҰДЬөДЎЈЯ@Т»ХВОТӮғҒн(lЁўi)ҢW(xuЁҰ)Б•(xЁӘ)ҪMәПЯүЭӢлҠВ·ЎЈЯ@Т»ХВКЗұҫХnіМөДЦШьc(diЁЈn)ғИ(nЁЁi)ИЭЦ®Т»

ОТӮғ?cЁЁ)ЪҢW(xuЁҰ)Б•(xЁӘ)•r(shЁӘ)°СЯ@Т»ХВөДғИ(nЁЁi)ИЭ·ЦһйЈә

Ўм4Ўў1 ЯүЭӢлҠВ·өД·ЦОц

Ўм4Ўў2 ЯүЭӢлҠВ·өДФO(shЁЁ)УӢ(jЁ¬)

Ўм4Ўў3 іЈУГөДҪMәПЯүЭӢ

Ўм4Ўў1 ҪMәПЯүЭӢлҠВ·өД·ЦОц

Т»ЈәҪMәПЯүЭӢлҠВ·өД·ЦОц ЈЁ1Ј©ЈәУРҪo¶ЁөДЯүЭӢлҠВ·ҲDЈ¬Ң‘(xiЁ§)іцЭ”іц¶ЛөДЯүЭӢұнЯ_(dЁў)КҪЈ» ЈЁ2Ј©ЈәБРіцХжЦөұнЈ» ЈЁ3Ј©ЈәНЁЯ^(guЁ°)ХжЦөұнёЕАЁіцЯүЭӢ№ҰДЬЈ¬ҝҙФӯлҠВ·КЗІ»КЗЧоАнПлЈ¬ИфІ»КЗЈ¬„tҢҰ(duЁ¬)ЖдЯM(jЁ¬n)РРёДЯM(jЁ¬n)Ј»

ОТӮғҢҰ(duЁ¬)ҪMәПЯүЭӢлҠВ·өД·ЦОц·ЦТФПВҺЧӮҖ(gЁЁ)ІҪуEЈә

ЎЈ өЪТ»ІҪЈәҢ‘(xiЁ§)ЯүЭӢұнЯ_(dЁў)КҪЎЈОТӮғУЙЗ°јү(jЁӘ)өҪәујү(jЁӘ)Ң‘(xiЁ§)іцёчйT(mЁҰn)ЯүЭӢұнЯ_(dЁў)КҪ

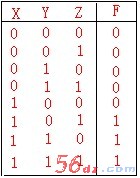

Аэ1ЈәТСЦӘУТГжөДЯүЭӢлҠВ·ҲDЈ¬ФҮ·ЦОцЖд№ҰДЬЎЈ

P=A+B S=A+P=AB W=B+P=AB

F=S+W=AB+A B

өЪ¶юІҪЈәБРХжЦөұнЈЁИзУТҲDЛщКҫЈ©ЎЈ

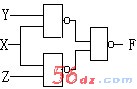

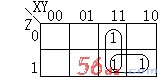

өЪИэІҪЈәЯүЭӢ№ҰДЬГиКцІўёДЯM(jЁ¬n)ФO(shЁЁ)УӢ(jЁ¬)ЎЈ

ҸДХжЦөұнЦРҝЙТФҝҙіцЯ@КЗТ»ӮҖ(gЁЁ)¶юЧғБҝЎ°Н¬»тЎұлҠВ·ЎЈФӯлҠВ·ФO(shЁЁ)УӢ(jЁ¬)І»әПАнЈ¬ЛьЦ»РиТ»ӮҖ(gЁЁ)"Н¬»т"йT(mЁҰn)јҙҝЙ.

Ўм4Ўў2 ҪMәПЯүЭӢлҠВ·өДФO(shЁЁ)УӢ(jЁ¬)

Т»ЈәҪMәПлҠВ·ЯүЭӢлҠВ·өДФO(shЁЁ)УӢ(jЁ¬)

лҠВ·ФO(shЁЁ)УӢ(jЁ¬)өДИО„Х(wЁҙ)ҫНКЗёщ“ю(jЁҙ)№ҰДЬФO(shЁЁ)УӢ(jЁ¬)лҠВ·Ј¬Т»°г°ҙИзПВөДІҪуEЯM(jЁ¬n)РРЈә

ЈЁ1Ј©°СЯүЭӢГьо}“QһйХжЦөұнЈ»Я@Т»ІҪОТӮғТӘҸДТФПВҺЧӮҖ(gЁЁ)·ҙГжҝј‘]

УГУўОДЧЦДёҙъұнЭ”Ил»тЭ”іцЈ»

·ЦЗеҺЧӮҖ(gЁЁ)Э”ИлЎўЭ”іцЈ»

·ЦЗеЭ”ИләНЭ”іцЦ®йgөДҢҰ(duЁ¬)‘Ә(yЁ©ng)кP(guЁЎn)ПөЎЈ

ЈЁ2Ј©°СЯүЭӢәҜ”ө(shЁҙ)ЯM(jЁ¬n)РР»ҜәҶ(jiЁЈn)Ј¬»ҜәҶ(jiЁЈn)өДРОКҪ„tКЗёщ“ю(jЁҙ)ЛщЯxУГөДЯүЭӢйT(mЁҰn)Ғн(lЁўi)ӣQ¶ЁЈ»

ЈЁ3Ј©ёщ“ю(jЁҙ)»ҜәҶ(jiЁЈn)ҪY(jiЁҰ)№ыәНЛщЯx¶ЁөДйT(mЁҰn)лҠВ·Ј¬®Ӣ(huЁӨ)іцЯүЭӢлҠВ·ҲDЎЈ

АэЈә ФO(shЁЁ)УӢ(jЁ¬)ИэЧғБҝұнӣQЖчЈ¬ЖдЦРXҫЯУР·сӣQҷа(quЁўn)ЎЈ

өЪТ»ІҪЈәБРіцХжЦөұнЎЈЈЁИзУТЙПҲDЈ©

ФO(shЁЁ)XЎўYЎўZ·Ц„eҙъұн…ўјУұнӣQөДЧғБҝЈ»FһйұнӣQҪY(jiЁҰ)№ыЈ¬

ОТӮғ°СЧғБҝТҺ(guЁ©)¶ЁһйЈәXЎўYЎўZһй1ұнКҫЩқіЙЈ»һй0ұнКҫ·ҙҢҰ(duЁ¬)ЎЈ

Fһй1ұнКҫНЁЯ^(guЁ°)Ј»һй0ұнКҫұ»·сӣQЎЈ

өЪ¶юІҪЈә»ҜәҶ(jiЁЈn)ЯүЭӢәҜ”ө(shЁҙ)ЎЈ

ОТӮғЯxУГЕc·ЗЯүЭӢҒн(lЁўi)ҢҚ(shЁӘ)¬F(xiЁӨn)ЎЈУГҝЁЦZҲDҒн(lЁўi)»ҜәҶ(jiЁЈn)ЈЁИзУТЦРҲDЈ©F=![]()

өЪИэІҪЈә®Ӣ(huЁӨ)ЯүЭӢлҠВ·ЎЈЈЁИзУТҲDЈ©

Ўм4Ўў3 іЈУГөДҪMәПЯүЭӢ

іЈУГҪMәПЯүЭӢөД·Nоҗ(lЁЁi)әЬ¶аЈ¬ЦчТӘУРИ«јУЖчЎўЧgҙaЖчЎўҫҺҙaЖчЎў¶аВ·Яx“сЖчөИЈ¬ПВГжОТӮғ·Ц„e°СЛьӮғҪйҪBТ»ПВЎЈ

Т»Јә°лјУЖчәНИ«јУЖч

ФЪ”ө(shЁҙ)ЧЦПөҪy(tЁҜng)ЦРЛгРg(shЁҙ)Я\(yЁҙn)Лг¶јКЗАыУГјУ·ЁЯM(jЁ¬n)РРөДЈ¬ТтҙЛјУ·ЁЖчКЗ”ө(shЁҙ)ЧЦПөҪy(tЁҜng)ЦРЧо»щұҫөДЯ\(yЁҙn)ЛгҶОФӘЎЈУЙУЪ¶юЯM(jЁ¬n)ЦЖЯ\(yЁҙn)ЛгҝЙТФУГЯүЭӢЯ\(yЁҙn)ЛгҒн(lЁўi)ұнКҫЈ¬ТтҙЛОТӮғҝЙТФУГЯүЭӢФO(shЁЁ)УӢ(jЁ¬)өД·Ҫ·ЁҒн(lЁўi)ФO(shЁЁ)УӢ(jЁ¬)Я\(yЁҙn)ЛглҠВ·ЎЈјУ·ЁФЪ”ө(shЁҙ)ЧЦПөҪy(tЁҜng)ЦР·ЦһйИ«јУәН°лјУЈЁөЪТ»ХВОТӮғТСҪӣ(jЁ©ng)ҪйҪBБЛЈ©ЛщТФјУ·ЁЖчТІ·ЦһйИ«јУЖчәН°лјУЖчЎЈ

ЈЁ1Ј©°лјУЖчФO(shЁЁ)УӢ(jЁ¬)

°лјУЖчІ»ҝј‘]өНО»ПтұҫО»өДЯM(jЁ¬n)О»Ј¬ТтҙЛЛьУРғЙӮҖ(gЁЁ)Э”Ил¶ЛәНғЙӮҖ(gЁЁ)Э”іц¶ЛЎЈ

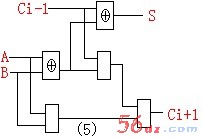

ФO(shЁЁ)јУ”ө(shЁҙ)ЈЁЭ”Ил¶ЛЈ©һйAЎўB Ј»әНһйS Ј»ПтёЯО»өДЯM(jЁ¬n)О»һйCi+1ЎЈ

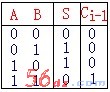

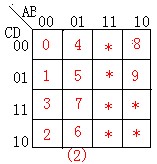

ЛьөДХжЦөұнһйЈәИзУТҲDЛщКҫ

әҜ”ө(shЁҙ)өДЯүЭӢұнЯ_(dЁў)КҪһйЈә S=AB+AB Ј» Ci+1=AB

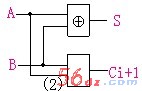

ЯүЭӢлҠВ·ҲDЈЁУГ®җ»тйT(mЁҰn)әНЕcйT(mЁҰn)ҳӢ(gЁ°u)іЙЈ©һйЈәИзУТҲD(2)ЛщКҫ

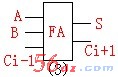

ЈЁ2Ј©И«јУЖчөДФO(shЁЁ)УӢ(jЁ¬)ЈЁЛьөДЯүЭӢ·ыМ–(hЁӨo)һйҲD(3)ЛщКҫЈ©

УЙУЪИ«јУЖчҝј‘]өНО»ПтёЯО»өДЯM(jЁ¬n)О»Ј¬ЛщТФЛьУРИэӮҖ(gЁЁ)Э”Ил¶ЛәНғЙӮҖ(gЁЁ)Э”іц¶ЛЎЈ

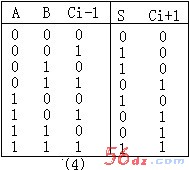

ФO(shЁЁ)Э”ИлЧғБҝһйЈЁјУ”ө(shЁҙ)Ј©AЎўBЎў Ci-1Ј¬Э”іцЧғБҝһй SЎў Ci+1

ЛьөДХжЦөұнһйЈәИзҲD(4)ЛщКҫ

әҜ”ө(shЁҙ)өДЯүЭӢұнЯ_(dЁў)КҪһйЈәS=ABCi-1+ABCi-1+ABCi-1+ABCi-1=A![]() B

B![]() Ci-1

Ci-1

Ci+1=ABCi-1+ABCi-1+ABCi-1+ABCi-1 =ЈЁA![]() BЈ©Ci-1+AB

BЈ©Ci-1+AB

ЯүЭӢлҠВ·ҲD(УГ®җ»тәНЕcйT(mЁҰn)ҳӢ(gЁ°u)іЙЈ©һйЈәИзҲD(5)ЛщКҫ

ЈЁ3Ј©И«јУЖчөД‘Ә(yЁ©ng)УГ

Тт?yЁӨn)йјУ·ЁЖчКЗ”?shЁҙ)ЧЦПөҪy(tЁҜng)ЦРЧо»щұҫөДЯүЭӢЖчјюЈ¬ЛщТФЛьөД‘Ә(yЁ©ng)УГәЬҸVЎЈЛьҝЙУГУЪ¶юЯM(jЁ¬n)ЦЖөДңp·ЁЯ\(yЁҙn)ЛгЎўіЛ·ЁЯ\(yЁҙn)ЛгЈ¬BCDҙaөДјУЎўңp·ЁЈ¬ҙaҪMЧғ“QЈ¬”ө(shЁҙ)ҙaұИЭ^өИЎЈ

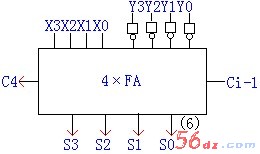

Аэ 1ЈәУГИ«јУЖчҳӢ(gЁ°u)іЙ¶юЯM(jЁ¬n)ЦЖңp·ЁЖчЎЈ

ТФЛДО»¶юЯM(jЁ¬n)ЦЖһйАэЎЈЈЁңp·ЁҝЙЮD(zhuЁЈn)“QһйјУСa(bЁі)Я\(yЁҙn)ЛгЈ©

ФO(shЁЁ)ғЙҪMЛДО»¶юЯM(jЁ¬n)ЦЖ·Ц„eһйX3X2X1X0әНY3Y2Y1Y0,°СY3Y2Y1Y0ПИЯM(jЁ¬n)РРЗуСa(bЁі)И»әуФЩЯM(jЁ¬n)РРјУ·ЁЯ\(yЁҙn)ЛгЎЈ

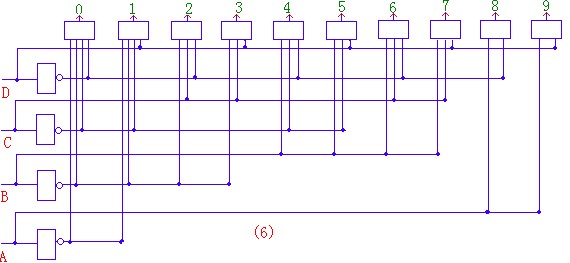

Тт?yЁӨn)йЗуСa(bЁі)КЗЦрО»Зу·ҙәуФЩјУЎ°1ЎұЛщТФЛьөДЯүЭӢлҠВ·ҲDһйИзҲD(6)ЛщКҫ:

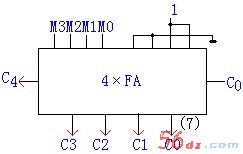

Аэ 2ЈәІЙУГЛДО»И«јУЖчНкіЙ8421BCDҙaЮD(zhuЁЈn)“QһйУа3ҙъҙaЎЈ

УЙУЪ8421BCDҙaјУ0011јҙһйУа3ҙъҙaЈ¬ТтҙЛЮD(zhuЁЈn)“QлҠВ·ҫНКЗјУ·ЁлҠВ·ЎЈ

ФO(shЁЁ)8421BCDҙaЛДО»УЦёЯО»өҪөНО»һйM3ЎўM2ЎўM1ЎўM0Ј¬Уа3ҙъҙaөДЛДО»УЙёЯөҪөНһйC3ЎўC2ЎўC1ЎўC0 ЎЈ

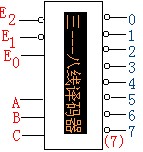

ЛьөДЯүЭӢлҠВ·ҲDһйИзҲD(7)ЛщКҫ:

¶юЈәҫҺҙaЖчәНЧgҙaЖч

Цё¶Ё¶юЯM(jЁ¬n)ЦЖҙъҙaҙъұнМШ¶ЁөДРЕМ–(hЁӨo)өДЯ^(guЁ°)іМҫНҪРҫҺҙaЎЈ°СДіТ»ҪM¶юЯM(jЁ¬n)ЦЖҙъҙaөДМШ¶Ёә¬БxЧgіцөДЯ^(guЁ°)іМҪРЧgҙaЎЈ

ЈЁ1Ј©ҫҺҙaЖч Тт?yЁӨn)йnО»¶юЯM(jЁ¬n)ЦЖ”ө(shЁҙ)ҙaУР2n·N о‘B(tЁӨi)Ј¬ЛщТФЛьҝЙҙъұн2nҪMРЕПўЎЈОТӮғ?cЁЁ)ЪҫҺҙaЯ^(guЁ°)іМЦРТ»°гКЗІЙУГҫҺҙaҫШкҮәНҫҺҙaұнЈ¬ҫҺҙaҫШкҮҫНКЗФЪҝЁЦZҲDЙПЦё¶ЁГҝТ»·ҪёсҙъұнДіТ»ЧФИ»”ө(shЁҙ)Ј¬°СЯ@Р©ЧФИ»”ө(shЁҙ)МоИлПа‘Ә(yЁ©ng)өД·ҪёсЎЈ

Аэ 1Јә°С0Ўў1Ўў2Ўў...Ўў9ҫҺһй5421BCDҙa.

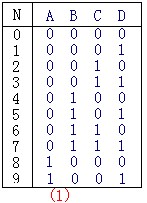

ПИҒн(lЁўi)ҙ_¶ЁҫҺҙaұнИзҲD(1)ЛщКҫәНҫҺҙaҫШкҮИзҲD(2)ЛщКҫ:

УЙҫҺҙaұнҙ_¶ЁёчЭ”іц¶ЛөДЯүЭӢұнЯ_(dЁў)КҪКЗЈә

A=5+6+7+8+9

B=4+9

C=2+3+7+8

D=1+3+6+8

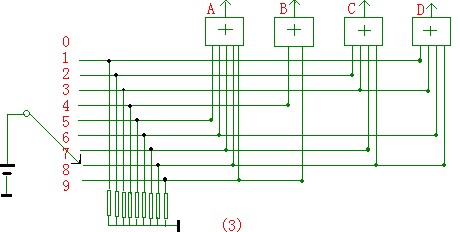

ёщ“ю(jЁҙ)Я@Р©ұнЯ_(dЁў)КҪҝЙУГ»тйT(mЁҰn)ҪMіЙ

ЯүЭӢлҠВ·ИзҲD(3)ЛщКҫ:

ЈЁ2Ј©ЈәЧgҙaЖч ҫҺҙaөДДжЯ^(guЁ°)іМҫНКЗЧgҙaЎЈ

ЧgҙaҫНКЗ°СҙъҙaЧgһйТ»¶ЁөДЭ”іцРЕМ–(hЁӨo)Ј¬ТФұнКҫЛьөДФӯТвЎЈҢҚ(shЁӘ)¬F(xiЁӨn)ЧgҙaөДлҠВ·ҫНКЗЧgҙaЖчЎЈ

ЧgҙaЖчҝЙ·Цһй¶юЯM(jЁ¬n)ЦЖЧgҙaЖчЎўК®ЯM(jЁ¬n)ЦЖЧgҙaЖчЎўјҜіЙЧgҙaЖчәН”ө(shЁҙ)ЧЦп@КҫЧgҙaтҢ(qЁұ)„У(dЁ°ng)лҠВ·ЎЈЖдЦР¶юЯM(jЁ¬n)ЦЖЧgҙaЖчКЗТ»·NЧоәҶ(jiЁЈn)ҶОөДЧғБҝЧgҙaЖч,ЛьөДЭ”іц¶ЛИ«КЗЧоРЎн—(xiЁӨng)ЎЈ

Аэ 2ЈәФO(shЁЁ)УӢ(jЁ¬)Т»ЧgҙaлҠВ·°С8421BCDҙaөД0Ўў1Ўў2Ўў...Ўў9ЧgіцҒн(lЁўi).

ЛДО»¶юЯM(jЁ¬n)ЦЖУРК®Бщ·N о‘B(tЁӨi)Ј¬¶шҢҚ(shЁӘ)лHЦ»РиТӘК®·NЈ¬ТтҙЛЖдУан—(xiЁӨng)Ччҹo(wЁІ)кP(guЁЎn)н—(xiЁӨng)ҝј‘].

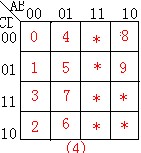

ЖдҫҺҙaҫШкҮһйИзҲD(4)ЛщКҫ.

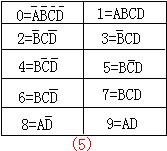

ОТӮғНЁЯ^(guЁ°)ҫҺҙaҫШкҮҝЙөГИзПВЧgҙaкP(guЁЎn)ПөЈәИзҲD(5)ЛщКҫ.

ЛщТФЛьөДЯүЭӢлҠВ·ҲDһйЈЁУГЕcйT(mЁҰn)әНЕc·ЗйT(mЁҰn)ҢҚ(shЁӘ)¬F(xiЁӨn)Ј©

ИзҲD(6)ЛщКҫ:

јҜіЙЧgҙaЖчөД№ӨЧчФӯАнЕcЖдЛьЧgҙaЖчТ»ҳУЈ¬ө«ЛьУРЛьөДМШьc(diЁЈn).

ЛьөДМШьc(diЁЈn)һйЈә

Э”ИлІЙУГҫҸӣ_јү(jЁӘ);(ңpЭpРЕМ–(hЁӨo)Ш“(fЁҙ)Эd)

Э”іцһй·ҙҙa;өНлҠЖҪУРР§(ңpЭpЭ”іц№ҰВК)

ФцјУБЛК№ДЬ¶Л.(ұгУЪ”U(kuЁ°)Х№№ҰДЬ)

ДҝЗ°іЈУГөДөдРНөДјҜіЙЧgҙaЖчКЗИэ------°ЛЧgҙaЖчЎЈ

ЛьөДЯүЭӢ·ыМ–(hЁӨo)һй.ИзҲD(7)ЛщКҫ: ЧўЈәЖдЦРE0E1E2һйК№ДЬ¶ЛЈ¬Ц»УР®”(dЁЎng)E1ЎўE2һй0•r(shЁӘ)E0һй1•r(shЁӘ)ҙЛЧgҙaЖчІЕ№ӨЧчЎЈ

ИэЈә”ө(shЁҙ)“ю(jЁҙ)Яx“сЖчәН¶аВ··ЦЕдЖч

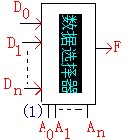

ЈЁ1Ј©”ө(shЁҙ)“ю(jЁҙ)Яx“сЖч ЛьҫНКЗҸД¶аӮҖ(gЁЁ)Э”Ил¶ЛЦРЯx“сТ»В·Э”іцЈ¬ЛьПа®”(dЁЎng)УЪТ»ӮҖ(gЁЁ)¶аВ·й_(kЁЎi)кP(guЁЎn)ЛьөДЯүЭӢ·ыМ–(hЁӨo)ИзҲD(1)ЛщКҫ:ЖдЦРD0D1ЎўЎўЎўDnКЗ”ө(shЁҙ)“ю(jЁҙ)Э”Ил¶Л;A0A1ЎўЎўЎўAnһйөШЦ·ЧғБҝЈЁУРnӮҖ(gЁЁ)өШЦ·ЧғБҝҫНУР2nӮҖ(gЁЁ)Э”Ил¶ЛЈ©.

ЈЁ1Ј©”ө(shЁҙ)“ю(jЁҙ)Яx“сЖч ЛьҫНКЗҸД¶аӮҖ(gЁЁ)Э”Ил¶ЛЦРЯx“сТ»В·Э”іцЈ¬ЛьПа®”(dЁЎng)УЪТ»ӮҖ(gЁЁ)¶аВ·й_(kЁЎi)кP(guЁЎn)ЛьөДЯүЭӢ·ыМ–(hЁӨo)ИзҲD(1)ЛщКҫ:ЖдЦРD0D1ЎўЎўЎўDnКЗ”ө(shЁҙ)“ю(jЁҙ)Э”Ил¶Л;A0A1ЎўЎўЎўAnһйөШЦ·ЧғБҝЈЁУРnӮҖ(gЁЁ)өШЦ·ЧғБҝҫНУР2nӮҖ(gЁЁ)Э”Ил¶ЛЈ©.

іЈУГөДУР¶юЯxТ»Ј¬ЛДЯxТ»Ј¬°ЛЯxТ»әНК®БщЯxТ»Ј¬ИфРиёь¶а„tУЙЙПКц”U(kuЁ°)Х№ЎЈ

Аэ 3ЈәИзҲD(2)ЛщКҫөДЛДЯxТ»”ө(shЁҙ)“ю(jЁҙ)Яx“сЖчЈ¬ФҮҢ‘(xiЁ§)іцЛьөДЭ”іцЯүЭӢұнЯ_(dЁў)КҪәН№ҰДЬұн

ЛьөДЯүЭӢЭ”іцұнЯ_(dЁў)КҪһй F=ЈЁA0A1D0+A0A1D1+A0A1D2+A0A1D3Ј©E

ЛьөД№ҰДЬұнһйЈәИзПВұнЛщКҫ

ҸДұнЙПОТӮғҝЙТФҝҙіц®”(dЁЎng)К№ДЬ¶ЛEһйЎ°1Ўұ•r(shЁӘ)Э”іцһйЎ°0ЎұјҙҪыЦ№Ј¬Ц»УР®”(dЁЎng)К№ДЬ¶ЛһйЎ°0Ўұ•r(shЁӘ)Яx“сЖчІЕУРР§ЎЈ

Аэ 4Јә°СЛДЯxТ»”U(kuЁ°)Х№һй°ЛЯxТ»ЎЈ

өШЦ·

К№ДЬ¶Л

Э”Ил

Э”іц

A0

A1

E

D

F

* *

1

*

0

0 0

0

D0---D3

D0

0 1

0

D0---D3

D1

1 0

0

D0---D3

D2

1 1

0

D0---D3

D3

°ЛЯxТ»ТӘУР°ЛӮҖ(gЁЁ)Э”ИлЧғБҝЈ¬ТтҙЛРиТӘИэӮҖ(gЁЁ)өШЦ·ЧғБҝ(ОТӮғ°СЖдЦРТ»ӮҖ(gЁЁ)A0ЧчһйК№ДЬ¶О)Ј»

ЛДЯxТ»Ц»ДЬУРЛДӮҖ(gЁЁ)Э”ИлЧғБҝЈ¬ЛщТФОТӮғРиТӘғЙӮҖ(gЁЁ)ЛДЯxТ»әНТ»ӮҖ(gЁЁ)·ЗйT(mЁҰn).·ЗйT(mЁҰn)өДЧчУГКЗёДЧғК№ДЬ¶ЛөДлҠЖҪЈ¬ңpЙЩК№ДЬ¶Л.ПИБРіцЛьөД№ҰДЬұнИзПВұнЛщКҫ:

ЯүЭӢлҠВ·ҲDИзҲD(3)ЛщКҫ:

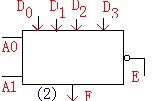

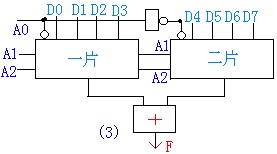

ЈЁ2Ј©¶аВ··ЦЕдЖч ЛьөД№ҰДЬКЗ°СЭ”Ил”ө(shЁҙ)“ю(jЁҙ)·ЦЕдҪoІ»Н¬өДНЁөАЙПЈ¬Па®”(dЁЎng)УЪТ»ӮҖ(gЁЁ)ҶОө¶¶а”Sй_(kЁЎi)кP(guЁЎn)ЎЈ

A0

A1

A2

D

F

0 0 0

D0----D7

D0

0 0 1

D0----D7

D1

0 1 0

D0----D7

D2

0 1 1

D0----D7

D3

1 0 0

D0----D7

D4

1 0 1

D0----D7

D5

1 1 0

D0----D7

D6

1 1 1

D0----D7

D7

·ө»Шн”Іҝ

·ө»Шн”Іҝ ЛўРВн“(yЁЁ)Гж

ЛўРВн“(yЁЁ)Гж ПВөҪн“(yЁЁ)өЧ

ПВөҪн“(yЁЁ)өЧ