NE555НщНBЃЌr(shЈЊ)ЛљМЏГЩыТЗ

NE555 ЃЈTimer ICЃЉщ8Ф_r(shЈЊ)ЛљМЏГЩыТЗЃЌДѓМsдк1971ФъгЩSignetics CorporationАl(fЈЁ)ВМЃЌдкЎ(dЈЁng)r(shЈЊ)ЪЧЮЈвЛЗЧГЃПьЫйЧвЩЬI(yЈЈ)ЛЏЕФTimer ICЁЃNE555ѓwЗeаЁЁЂжиСПнpЁЂЗ(wЈЇn)ЖЈПЩППЃЌВйзїыдДЗЖњДѓЃЌнГіЖЫЕФЙЉНoыСїФмСІ(qiЈЂng)ЃЌг(jЈЌ)r(shЈЊ)ОЋД_ЖШИпЃЌиЖШЗ(wЈЇn)ЖЈЖШМбЃЌЧвr(jiЈЄ)ИёБувЫ ЁЃ555ЖЈr(shЈЊ)ЦїЪЧвЛЗNЊ(yЈЉng)гУOщVЗКЕФжав(guЈЉ)ФЃМЏГЩыТЗЃЌдыТЗЪЙгУь`ЛюЁЂЗНБуЃЌжЛашЭтНгЩйСПЕФзшШндМўОЭПЩвд(gЈАu)ГЩЮЗ(wЈЇn)ЁЂЖржCКЭЪЉУмЬиг|Аl(fЈЁ)ЦїЁЃвђЖјVЗКгУгкаХЬ(hЈЄo)ЕФЎa(chЈЃn)ЩњЁЂзQЁЂПижЦКЭzy(cЈЈ)ЁЃ

ЁЁЁЁ1Ф_ЃКЭтНгыдДи(fЈД)OЛђНгЕиЃЈGNDЃЉЁЃ

ЁЁЁЁ2Ф_ЃКTRг|Аl(fЈЁ)нШыЁЃ

ЁЁЁЁ3Ф_ЃКнГіЖЫЃЈOUTЛђVoЃЉЁЃ

ЁЁЁЁ4Ф_ЃКRDЭ(fЈД)ЮЛЖЫЃЌвЦВНЧхСуЧвЕЭыЦНгааЇЃЌЎ(dЈЁng)НгЕЭыЦНr(shЈЊ)ЃЌВЛЙмTRЁЂTHнШыЪВУДЃЌыТЗПЪЧнГіЁА0ЁБЁЃвЊЯыЪЙыТЗе§ГЃЙЄзїЃЌt4Ф_Њ(yЈЉng)ХcыдДЯрпBЁЃ

ЁЁЁЁ5Ф_ЃКПижЦыКЖЫCOЃЈЛђVCЃЉЁЃШєДЫЖЫЭтНгыКЃЌtПЩИФзШ(nЈЈi)ВП?jЈЉ)Щ(gЈЈ)БШн^ЦїЕФЛљЪ(zhЈГn)ыКЃЌЎ(dЈЁng)дЖЫВЛгУr(shЈЊ)ЃЌЊ(yЈЉng)ЂдЖЫДЎШывЛжЛ0.01ІЬFыШнНгЕиЃЌвдЗРв§ШыИЩ_ЁЃ

ЁЁЁЁ6Ф_ЃКTHИпг|Аl(fЈЁ)ЖЫЃЈщжЕнШыЃЉЁЃ

ЁЁЁЁ7Ф_ЃКЗХыЖЫЁЃ

ЁЁЁЁ8Ф_ЃКЭтНгыдДVCCЃЈVDDЃЉЁЃ

ЃЈ2ЃЉ555ЙІФмНщНB

ЁЁЁЁ555ЖЈr(shЈЊ)ЦїЕФЙІФмжївЊЪЧгЩЩ(gЈЈ)БШн^ЦїC1КЭC2ЕФЙЄзї юrQЖЈЕФЁЃгЩD1ПЩжЊЃЌЎ(dЈЁng)V6ЁЗVAЁЂV2ЁЗVBr(shЈЊ)ЃЌБШн^ЦїC1ЕФнГіVC1=0ЁЂБШн^ЦїC2ЕФнГіVC2=1ЃЌЛљБОRSг|Аl(fЈЁ)ЦїБЛжУ0ЃЌTDЇ(dЈЃo)ЭЈЃЌЭЌr(shЈЊ)VOщЕЭыЦНЁЃ

ЁЁЁЁЎ(dЈЁng)V6ЁЖVAЁЂV2ЁЗVBr(shЈЊ)ЃЌVC1=1ЁЂVC2=1ЃЌг|Аl(fЈЁ)ЦїЕФ юB(tЈЄi)БЃГжВЛзЃЌвђЖјTDКЭнГіЕФ юB(tЈЄi)вВОSГжВЛзЁЃ

ЁЁЁЁЎ(dЈЁng)V6ЁЖVAЁЂV2ЁЖVBr(shЈЊ)ЃЌVC1=1ЁЂVC2=0ЃЌЙЪг|Аl(fЈЁ)ЦїБЛжУ1ЃЌVOщИпыЦНЃЌЭЌr(shЈЊ)TDНижЙЁЃ

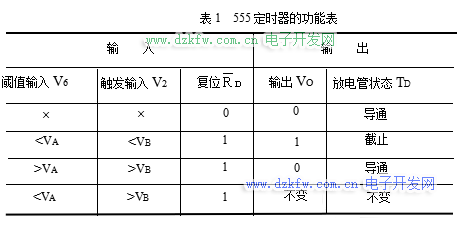

ЁЁЁЁп@гЮвОЭЕУЕНСЫБэ1 555ЖЈr(shЈЊ)ЦїЕФЙІФмБэЁЃ

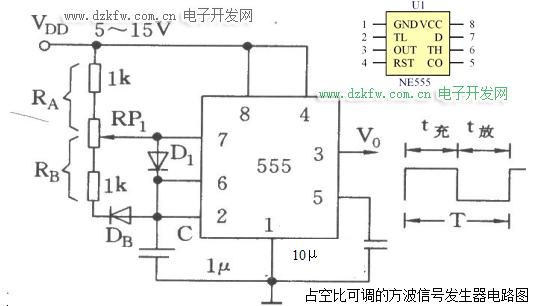

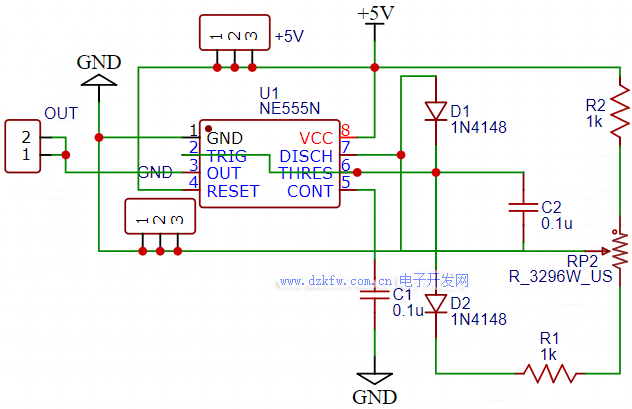

ЁЁЁЁ2ЁЂеМПеБШПЩе{(diЈЄo)ЕФЗНВЈаХЬ(hЈЄo)Аl(fЈЁ)ЩњЦї

ЁЁЁЁЃЈ1ЃЉеМПеБШПЩе{(diЈЄo)ЕФЗНВЈаХЬ(hЈЄo)Аl(fЈЁ)ЩњЦїыТЗD

ЁЁЁЁ

ЁЁЁЁD2 РћгУ555ЖЈr(shЈЊ)ЦїдO(shЈЈ)г(jЈЌ)ЗНВЈыТЗдРэD

ЁЁЁЁЃЈ2ЃЉеМПеБШПЩе{(diЈЄo)ЕФЗНВЈаХЬ(hЈЄo)Аl(fЈЁ)ЩњЦїЗжЮі

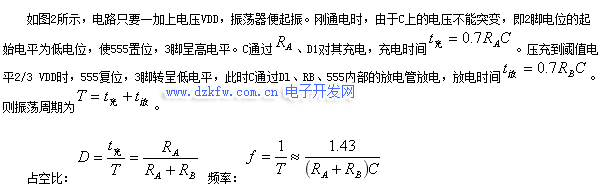

ЁЁЁЁ3ЁЂ(shЈЊ)ђ(yЈЄn)Е(shЈД)ў(jЈД)

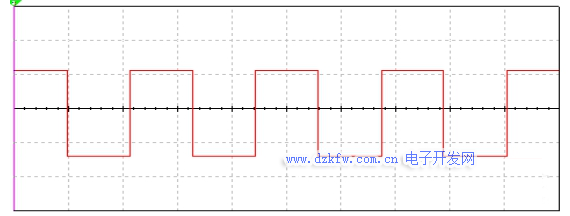

ЁЁЁЁЃЈ1ЃЉЗТецыТЗD

ЁЁЁЁ

ЁЁЁЁD3 MulTIsimыТЗD

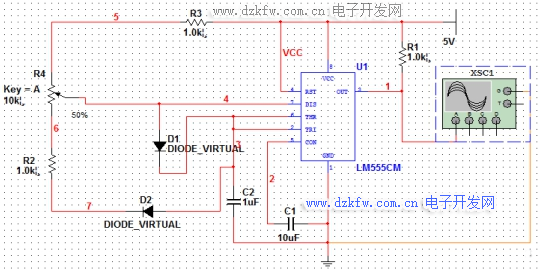

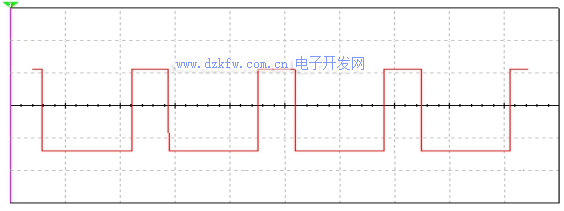

ЁЁЁЁЃЈ2ЃЉЗТецыТЗНY(jiЈІ)Йћ

ЁЁЁЁ

ЁЁЁЁD4 еМПеБШщ50%ЕФЗНВЈВЈаЮ

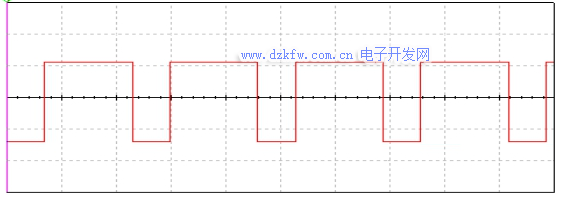

ЁЁЁЁ

ЁЁЁЁD5 еМПеБШаЁгк50%ЕФЗНВЈВЈаЮ

ЁЁЁЁ

ЁЁЁЁD6 еМПеБШДѓгк50%ЕФЗНВЈВЈаЮ

4СЂ(chuЈЄng)EDA

дРэD

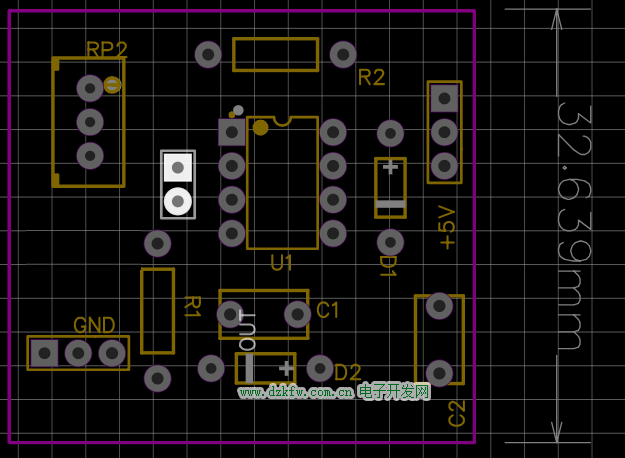

PCBдРэD

ЎPCBзЂвтЪТэ(xiЈЄng)ЃК

a.дРэDОТЗВЛФмгаНЛВцЃЛ

b.ОКЭщgОрдO(shЈЈ)щ0.762ЃЌИќШнвзЇ(dЈЃo)ЭЈаХЬ(hЈЄo)

c.яwОВЛФмФыШнЯТЗНзпп^

d.яwОВЛФмГЩ90Ёу

дгЩЃКжБНЧп@(gЈЈ)ЮЛжУPCBОЕФЖШАl(fЈЁ)ЩњСЫзЛЏ(ФЧзшПЙОЭў(huЈЌ)Аl(fЈЁ)ЩњзЛЏ)ЃЌў(huЈЌ)Ўa(chЈЃn)ЩњEMIИЩ_ЃЌМДыДХИЩ_ЁЃ

жБНЧЮЛў(huЈЌ)Ўa(chЈЃn)ЩњМФЩњыШнЃЌгАэаХЬ(hЈЄo)й|(zhЈЌ)СП(гАэзюДѓЕФОЭЪЧr(shЈЊ)чаХЬ(hЈЄo)ЕФЩЯЩ§r(shЈЊ)щgКЭЯТНЕr(shЈЊ)щg)

1ЁЂНoыдДфу~ПЩвдп^ИќДѓыСї

2ЁЂНoЕифу~ПЩвдpаЁаХЬ(hЈЄo)зшПЙЕФзїгУ

3ЁЂОЇеёЕзЯТфу~ЃЌЗРжЙОЇеёИпЫйаХЬ(hЈЄo)І(duЈЌ)жмњаХЬ(hЈЄo)Ўa(chЈЃn)ЩњИЩ_ЁЃ

4ЁЂОW(wЈЃng)Иёу~(ИпЫйаХЬ(hЈЄo))ЃЌ(shЈЊ)аФу~(зпДѓыСї)

дкNE555Ш§Ь(hЈЄo)в§Ф_ЃЈнГіФ_ЃЉашвЊЗХШыХХсЕФФПЕФЪЧщСЫзЪОВЈЦїг^ВьЫќ

ЗЕЛиэВП

ЗЕЛиэВП ЫЂаТэУц

ЫЂаТэУц ЯТЕНэЕз

ЯТЕНэЕз