移位寄存器不但可以寄存數碼,而且在移位脈沖作用下,寄存器中的數碼可根據需要向左或向右移動。移位寄存器也是數字系統和計算機中應用很廣泛的基本邏輯部件。

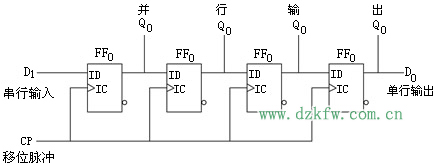

圖1所示電路是由邊沿D觸發器組成的4位移位寄存器。

由圖1可知,由第一個D觸發器FF0的輸入端接收輸入信號,其余的每個觸發器的輸入端均與前一個觸發器的輸出端相連。各觸發器的時鐘脈沖控制端與同一個時鐘脈沖CP信號相連,因此各觸發器的觸發時刻相同,都是CP脈沖的上升沿。

下面以4位二進制代碼1101為例,說明圖1所示移位寄存器的寄存過程。

二進制代碼1101以串行的方式從串行輸入端DI依次輸入。設各觸發器的初始狀態為零,即Q3Q2Q1Q0=0000。

|

| 圖1 由D觸發器組成的4位移位寄存器 |

首先,將第一個二進制碼“1”輸入串行輸入端DI。當移位脈沖CP的第一個上升沿到達時,個觸發器將各自的輸入端狀態傳輸到輸出端。由于從CP脈沖的上升沿到達開始到各觸發器次態的建立需要一段傳輸延時時間,因此當CP脈沖的上升沿同時作用于各觸發器時,各觸發器輸入端的狀態還沒有改變。于是FF3按Q2原來的狀態觸發,FF2按Q1原來的狀態觸發,FF1按Q0原來的狀態觸發,FF0按串行輸入端D1的狀態觸發。因此,當CP的第一個上升沿到達后,各觸發器的狀態變為Q3Q2Q1Q0=0001。

同理,將第二個二進制數碼“1”送入串行輸入端D1,當CP的第二個上升沿到達時,各觸發器的狀態變為Q3Q2Q1Q0=0011。以此類推,當第4個移位脈沖過后,將這4個二進制代碼儲存到了4個觸發器的輸入端Q3Q2Q1Q0=1101。

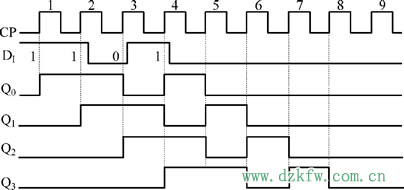

移位數據寄存情況如表1所示。也可以用波形圖的形式表示移位寄存器的數據寄存情況,如圖2所示。

| 表1 移位寄存器的移位寄存過程 |

| CP脈沖 | 串行輸入DI | Q3 | Q2 | Q1 | Q4 |

| 0 | × | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

| 2 | 1 | 0 | 0 | 1 | 1 |

| 3 | 0 | 0 | 1 | 1 | 0 |

| 4 | 1 | 1 | 1 | 0 | 1 |

|

| 圖2 圖1電路的波形圖 |

從圖6-5-3所示的波形圖可以看出,經過4個CP脈沖后,串行輸入的4位二進制代碼全部已入了移位寄存器中,同時可以從4個觸發器的輸出端同時輸出這4為二進制代碼。如果繼續加入4個CP脈沖,則可以從串行輸入-并行輸出和串行輸出入-串行輸出。由于在移位脈沖的作用下,二進制代碼在移位寄存器中依次右移,所以又稱為右移移位寄存器。當移位寄存器的電路實現的是在移位脈沖的作用下,二進制代碼在移位寄存器中依次左移,這種寄存器稱為左移移位寄存器。

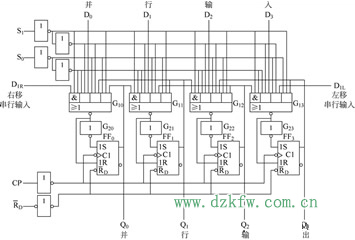

為了便于擴展移位寄存器的功能和增加使用的靈活性,在定型生產的移位寄存器集成電路上有的又附加了左移、右移控制,并行數據輸入、保持、異步置零(復位)等功能。圖3所示為4位雙向移位寄存器74LS194的邏輯電路和圖形符號。

|

|

| 圖3(a) 邏輯圖 | 圖3(b) 圖形符號 |

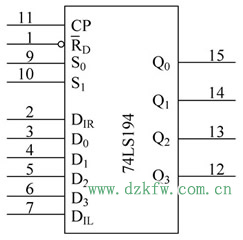

由圖3所示,雙向移位寄存器74LS194由4個RS觸發器和輸入控制電路組成。DIR為數據右移串行輸入端,DIL為數據左移串行輸入端,D0~D3為數據并行輸入端,Q0~Q3為數據并行輸出端,同時Q3還可以作為數據串行輸出端,CP為移位脈沖控制端![]() 為清零端,移位寄存器正常工作時該端置“1”,S0、S1為雙向移位寄存器的工作狀態控制端。

為清零端,移位寄存器正常工作時該端置“1”,S0、S1為雙向移位寄存器的工作狀態控制端。

74LS194既可以實現串行輸入,也可以并行輸入;既可以實現串行輸出,也可以并行輸出,在串行寄存方式中,既可以實現右移寄存,也可以實現左移寄存,還可以保持數據不變。74LS194雙向移位寄存器的這些工作狀態都是由控制端S0、S1實現的,如表1所示。表1稱為74S194的邏輯功能表。

| 表1 74LS194的邏輯功能表 |

| S1 | S4 | 工作狀態 | |

| 0 | × | × | 置零 |

| 1 | 0 | 0 | 保持 |

| 1 | 0 | 1 | 右移 |

| 1 | 1 | 0 | 左移 |

| 1 | 1 | 1 | 并行輸入 |

當S1=S0=0時,移位寄存器處于數據保持狀態。此時不論輸入端和移位脈沖輸入端有何變化,移位寄存器各輸出端的狀態保持不變。

當S1=0,S0=1時,移位寄存器保持右移寄存狀態。隨著位移脈沖的到來,右移串行輸入端DIR的數據依次寄存到寄存器中,并且移位寄存器中的數據依次右移。

當S1=1,S0=0時,移位寄存器處于左移寄存狀態。隨著移位脈沖的到來,左移串行輸入端DIL的數據依次寄存到寄存器中,并且移位寄存器中的數據依次左移。

當S1=1,S0=1時,位移寄存器處于并行輸入寄存狀態。此時串行輸入端的數據不起任何作用。當移位脈沖CP來一個脈沖時,寄存器將并行輸入端D0~D3的數據并行輸入到并行輸出端Q0~Q3。

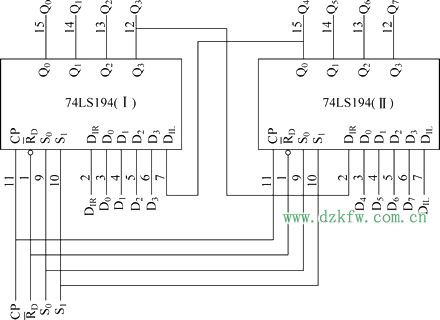

例1 用兩片4位雙向移位寄存器74LS194接成一個8位雙向移位寄存器。

解 所要涉及的8位雙向移位寄存器需要完成8位二制數據的寄存,因此需要由兩片4位雙向移位寄存器74LS194組成。同時,8位雙向移位寄存器應具備4位雙向移位寄存器所有的邏輯功能,即能實現并行輸入、左移寄存、右移寄存、數據保持和異步清零等功能。

如圖4所示,通過分析,將兩片4位雙向移位寄存器的輸入和輸出同時作為8位雙向移位寄存器的輸入和輸出。將74LS194(I)的右移串行輸入端作為8位雙向移位寄存器的右移串行輸入端,同時將74LS194(I)的串行輸出端與右側74LS194(II)的右移串行輸入端相連。同樣,將74LS194(II)的左移輸入端作為8位雙向移位寄存器的左移串行輸出端,同時將74LS194(II)的串行輸出端與74LS194(I)的左移串行輸入端相連。將兩片4位雙向移位寄存器的移位脈沖輸入端、清零端和工作狀態輸入端分別相連。這樣,就實現了用兩片4位雙向移位寄存器74LS19474LS194接成一個8位雙向移位寄存器。

|

| 圖4 例1的電路圖 |

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底