毫米波長范圍(30-300GHz)內除了其較低端外,還沒有很好地被利用。而在成像,安全,醫療,和短距離無線傳輸以及數據速率不斷提高的光纖傳輸中的新應用可能會迅速地改變這種狀態[1],[2]。在過去的三十年里,III-V 技術(GaAs 和InP)已經逐漸擴大到這個毫米波范圍中。新近以來,由于工藝尺寸持續不斷地減小,硅技術已經加入了這個“游戲”。

在本文中,按照半導體特性和器件要求,對可用于100-GHz 和100-Gb/s 應用的半導體有源器件進行了綜述。隨后介紹了使用最廣泛的技術,接著是兩個不同方面具有競爭性的技術現狀:分頻器,來說明該技術適宜用在高速數字電路中,以及振蕩器,用來說明其在模擬電路應用中的性能。

材料和工藝的基本特性

半導體材料的特性

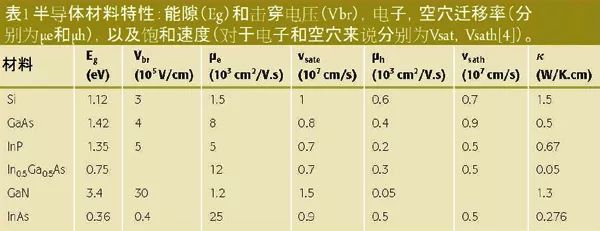

運行在很高頻率下的電子器件所表現的性能主要與:1)組成半導體的材料特性和2)器件的結構有關[3]。Si,GaAs 和InP 是目前具有截止頻率在300GHz 及以上的器件所選擇的材料。在表1,人們給出了一些相關的表征能隙,載流子輸運特性和導熱性的參數。同樣也報道了與InP,GaN 和InAs 晶格相匹配的InGaAs 的特性。

擁有一個足夠大能隙(Eg>1eV )是很有利的,這是因為它可以提供好的擊穿特性。Si,GaAs 和InP 在100nm 實際上可以承受幾伏的電壓水平;此外,p-n 結顯示出很明晰的整流行為,室溫下的泄漏電流可以忽略不計。采用GaN 可以獲得更高的擊穿電壓,InAs 因為其能隙很低而只能用于電壓很低的器件。

III-V 材料中的電子遷移率比硅的要大,這意味著在給定的摻雜濃度下,n-型接觸區具有較低的串聯電阻,而對于p-型 區來說,由于III-V 材料較低的空穴遷移率,情況則恰恰相反。然而,在器件的高場強區控制跨導和渡越時間的載流子速度與取決于載流子類型的飽和漂移速度相接近(Vsat 或Vsath′取決于載流子的類型;接近于10nm/ps)。由于暫態效應(電子從導帶中的低能級,高遷移率能谷到達較高能級,較低遷移率能谷的轉換不是瞬間發生的),電子的傳輸通常會受益于一些過沖量;例如,根據具有薄集電極的InP異質結雙極性晶體管(HBT)的基極到集電極的渡越時間所推導出的有效速度大于3×107cm/s,大約是飽和速度的5 倍[5]。

甚高頻率性能意味著較短的渡越時間和較低的RC寄生量;對于場效應管(FET)和雙極性晶體管來說,這通常可以通過減小電子器件的尺寸和提高電流密度來實現(例如,見[6])。對于極高頻器件和電路來說,熱導率則成為一個重要的參數,硅在與其III-V 技術的對手相比時,其所具有的良好的導熱性便成為一個真正的優勢,因為這有可能達到更高的器件密度。

基于III-V 技術的早期單片微波集成電路(MMIC)的主要優點之一要歸因于未摻雜(或補償)基片的半絕緣特性,這是與其大的半導體能隙直接相關的(基片的電阻率為108Ω.cm 的數量級,而硅的電阻率為104Ω.cm)。這使得可以實現具有低關聯寄生效應的電阻,電感和傳輸線。隨著近來巨大的微波應用市場的開發(例如,移動電話網絡),在硅基技術上引入無源器件這方面已經取得了很大的進展。此外,絕緣體加載硅基片技術(SOI)已經展示出其降低寄生效應的潛力(然而,這是以較低的基片導熱率為代價的)。

服務于高頻應用的FET 和雙極性晶體管

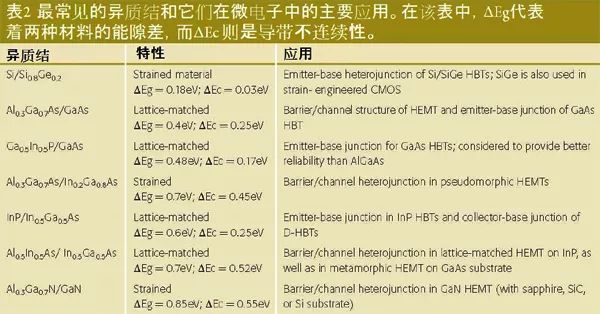

今天,適用于高頻應用的雙極性晶體管和FET 是基于異質結結構的(除了是硅基MOSFET 以外)。對異質結的開發已經有40 多年了,并且在材料和晶格應力方面還在不斷地發展著。兩種不同材料(具有同樣的晶體結構和同樣的晶格參數)之間的異質結主要是由它們的能隙差異,以及由這種差異所區分的導帶和價帶的階躍方式來表征的(表2)。在晶體管的有源區,異質結被用來達到兩個不同的目的:

• 不論它們各自的摻雜濃度如何,保證雙極性晶體管中從發射極向基極注入的是電子占主導地位的載流子• 在高電子遷移率晶體管(HEMT)中將電子局限在未摻雜的量子肼中。

雖然最初是針對晶格匹配異質結來實施的,但很快就顯示出用在失配異質結中也可以增強性能,條件是應力結晶層是在假晶厚度的極限內(如果生長層足夠薄,其晶格常數會調整到基片的晶格常數)。這種特性被用在HBT 中(例如漸變組分的方法,graded-composition)來生成具有短的渡越時間的基極層,以及高遷移率HEMT 的溝道層。在臨界厚度以上,(失配程度越高,層厚就越薄),生長層松弛下來,在晶體結構中便會出現晶格脫位。這種現象仍然可以被用來在基片的頂部生成具有不同晶格參數的高質量晶體層,在中間有一個過渡層(緩沖層)來俘獲大多數的脫位。例如,這種結構可以在被稱為改性(metamorphic)HEMT 中找到,在松弛緩沖層之上又生長了一層高質量的活性異質結構。特別是,變性結構允許采用極高遷移率的InAs 溝道[7],[8]。

目前,可以預見幾種服務于100-GHz 和100-Gb/s應用的技術:GaAs 和InP HEMT;InP 和SiGe HBT,這些技術在過去的十年中已經在使用之中了;以及硅CMOS 技術,從最近的一些情況來看,它似乎要發揮作用了。很有前景的技術如GaN HEMT 以及那些采用小能隙材料的技術同樣可以進入這個“游戲”。到目前為止,由于GaN HEMT 非凡的微波和毫米波功率容量,人們已對其進行了開發[9]。此外,與晶體結構相關的壓電效應所帶來的高界面電子密度(大約1013cm-2)可以用來補償相對較低的載流子遷移率,如果特定的結構設計可以產生低接觸電阻的話,那么使其具有甚高頻率性能似乎也是可行的[10]。

HBT 與FET 的差別

除了FET 是單極性器件以外(只有一種類型的載流子參與晶體管的運行,而一個雙極性器件則意味著兩種類型的載流子都參與運行),在雙極性和FET 技術之間還可以觀察到幾種差別,特別是:

• HBT 器件具有指數性的驅動特性[就是說,集電極電流與輸入電壓之間的依賴關系是指數性的:icαexp(Vbe/kT)],而FET 器件的則是平方的關系[漏極電流隨著電壓的平方而變化的:idsαk(Vgs2)]。對于HEMT 來說,這種關系轉化為具有較大分散性的門限電壓。這便是為什么高速數字或混合信號集成電路(IC)通常采用HBT 技術進行設計的原因(但請記住CMOS 在數字集成電路芯片中的成功)。另一方面,HEMT 呈現出比雙極晶體管較低的微波噪聲(金屬柵極電阻比半導體基極電阻要低)。

• HBT 晶體管是一個工作在很高電流密度下的垂直溝道器件(>100KA/m2,具有最高截止頻率的HBT 的電流密度甚至>1MA/cm2)。由于其所具有的高相關熱阻,HBT 的高功耗會削弱其固有的低門限電壓分散性這個優點。

• 雖然截止頻率可以是類似的(直到500GHz),微波雙極晶體管通常是具有較低阻抗的器件,這是由較高的跨導和輸入電容來表征的。這會產生一些后果,包括雙極晶體管較低的負載靈敏度。

現有工藝

雖然一個設計人員可能不容易接觸到不同的工藝,但還是存在一些為數不多的具有下列工藝的制造廠家:

• 45-,65-和90-nm CMOS• 130- nm HBT SiGe• 100- nm HEMT• 500- nm HBT InP。

對GaAs HEMT 的開發已經很長時間了,其柵極長度遠遠小于1μm;就較早的MESFET 技術而言,主要的技術變化是與更加復雜的異質外延結構相關的。類似地,III-V HBT 技術通過將低頻GaAs 功率放大器用于手機之中而取得了商業上的成功。只需通過轉換到InP 基的材料系統,這個技術便可踏入甚高頻領域。

新近,由于晶體管尺寸持續不斷地下降,硅工藝也同樣登上了毫米波舞臺。當SiGe HBT 技術被開發后,這種技術通過深亞毫米工藝被引入到Bi-CMOS 圓晶廠,很快便呈現出具有與它們所對應的III-V 技術相近的截止頻率。今天,這兩個技術主要的不同之處是:1)SiGe HBT 技術具有更成熟的工業環境(較高的電路復雜程度和擴展了CMOS 的環境),以及2)該工藝較低的集電極擊穿電壓。

當談到應用時,決定哪種工藝最適合的主要因素可能是下面幾點,各自的分量取決于應用情況。

1) 性能。這是一個關鍵因素,特別是對于那些要求具有最佳性能的應用來說。2) 目標規范。應用的規范要求可能會改變(隨著標準的演變),對于新應用來說,具有一定程度的靈活性也許是必要的。3) 直流功耗。為了減少設備的尺寸以及移動終端的重量和功耗,低功耗是一個重要的因素。4) 門數。這是另一個重要方面,因為數字信號處理正在提高其在應用中的分量。5) 成本。很顯然這是一個很重要的問題,并且適用于整個系統。而成本反過來則取決于所需的器件數量(市場容量):對于小的或中等數量(幾千到幾萬件)來說,III-V 工藝可能比SiGe的成本要低;對于更大的數量,情況則可能相反。

成熟工藝的介紹及現狀

基于GaAs 和InP 的P-HEMT和M-HEMT

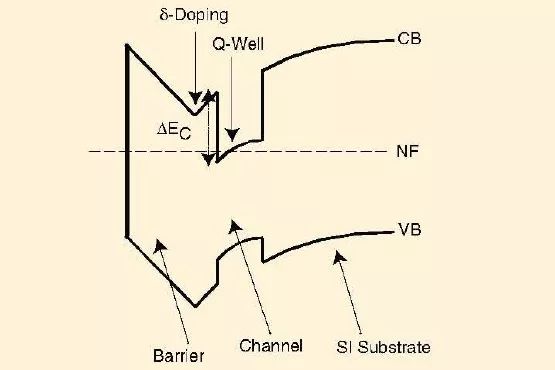

最初,GaAs 晶體管是具有n- 型溝道的肖特基柵FET(MESFET),因為III-V 材料中電子的遷移率比空穴的遷移率大得多。會妨礙實現MOS 結構的表面很強的費米能級釘扎效應卻有利于開發肖特基柵極。MESFET的性能通過提高溝道的摻雜濃度而逐漸改善;這是以電子遷移率(當摻雜濃度提高時,遷移率下降)和柵極泄漏電流為代價的。在1980 年所引入的HEMT 結構(見圖1) 可以同時實現兩種改善:1) 通過一個高遷移率溝道來提高溝道電流(產生一個高跨導),以及2)由于寬能隙勢壘而改善了柵極泄漏。

圖1、HEMT 異質結構的能帶圖展示了夾在半-絕緣(SI)基片和勢壘層之間的窄能隙溝道。在這個圖中,勢壘層是δ 摻雜,這意味著將施主雜質引入到一個極薄層內。溝道中的電子在界面的量子肼中積累,界面導帶偏移量(ΔEc)控制著表面密度ns。

自從HEMT 技術問世以來,人們已經引入了許多旨在改善性能(ns 和Vsate)的改進方案。兩種主要的途徑是:1)提高導帶偏移,從而使得在界面量子肼內積累更多的電子,以及2)提高溝道的遷移率,實際上這意味著提高InGaAs 溝道中In 成分的含量(從常規的GaAsHEMT 的Xin=0%到最高速InP HEMT 中的Xin=80%)。

目前,正在GaAs 基片上開發兩種類型的HEMT:

1) 具有一層AlGaAs 障礙層和一個應力InGaAs 溝道的主流GaAs P-HEMT(假晶HEMT)主要是用在20-70GHz 頻率范圍的低噪聲或功率應用中[11]。2) 采用GaAs M-HEMT(改性HEMT)可以獲得更高的速度,它基本上是一個在GaAs 基片的松弛緩沖層上生長一個晶格匹配的InP 結構(具有一個ALInAs/InGaAs 異質結結構)。這個結構得益于InP 基結構較高的速度和與較大,較脆GaAs 基片相關的低成本。雖然緩沖層的熱導性相當差,但這個技術在100GHz 下仍然顯示出出色的功率和噪聲性能。

就最高運行速度和較高的輸出功率而言,這些性能紀錄還是由InP PM-HEMT 來創造的,它在90GHz 時超過400mW,并且在300GHz 超過2mW[14]。

InP HBT

連同采用與InP 基片晶格匹配的材料系統成功制成了器件的首篇報道一起,在90 年代后期,有關InP 異質結雙極性晶體管(HBT)的工作正式邁入了軌道[15]。這個材料系統具有若干超出SiGe 和GaAs 的優勢,包括:

1) InGaAs(晶格與InP 相匹配)材料中的遷移率和電子速度比GaAs 或SiGe 的更高。2) 與GaAs 相比具有較低的表面復合速率,從而具有較高的電流增益,導致其具有按比例縮小到較小尺寸的能力。3) 由于在基極中使用了窄能隙InGaAs,則具有比GaAs 較低的基極-發射極開啟電壓。4) 當InP 被用作集電極材料時,具有比SiGe 更高的擊穿電場強度。5) 產品具有比其它任何Si 或III-V 材料更高的擊穿電場/截止頻率的乘積。6) 在InGaAs 基極和InGaAs 發射極覆蓋層(Cap)的最大摻雜濃度較高,從而產生較低的寄生接觸電阻值。7) 由于許多三價半導體材料的晶格與InP 的相匹配,從而具有一種增強的“用能隙來操縱”HBT 的能力。

這些年來,InP HBT 已經擔負起最快速基準晶體管和電路性能的重任。近來,在Santa Barbara 和illinois 的研究小組已經報道了Ft 超過700GHz 的器件,以及Ft/Fmax 超過500GHz 的平衡器件[16],[17]。

SiGe HBT-BiCMOS;CMOS 和NMOS

在80 年代后期所開發的SiGe HBT 是采用成熟的硅技術來生產的。通過各種開發,包括在基極使用碳摻雜和基極自對準生長技術,器件已達到了出色的性能- 特別是,在Bi-CMOS 配置中的HBT 顯示了高的Ft,Fmax(>300GHz)[19]。此外,由于具有很好的鈍化結而獲得了在混頻器和振蕩器中極為有用的出色的1/f 噪聲性能。所有這些特性被用來制成了許多可以運行的芯片,例如在43GHz 光纖傳輸系統中的多用復用器(MUX)和多路分離器(DEMUX),高速模-數轉換器[20],以及77GHz 頻率的車用雷達芯片組,甚至可用于工作在100GHz 以上的收發機中[21]。

在過去的幾年中,隨著極短柵極工藝過程的采納(現在是在45-90nm 的范圍),人們已經報道了具有極高截止頻率的n-溝道MOS 晶體管(ft>200GHz)[22]。這種與半導體國際技術發展藍圖相一致的結果,實際上是從前僅限于III-V HEMT(昂貴)的電子束加工工藝過程和許多正在發生的MOS 結構演變所產生的柵極長度減小的結果。正像HEMT 結構一樣,通過較高的遷移率溝道(例如所獲取的應變硅溝道)以及由所謂的高-K 電介質柵極所產生的具有合適的氧化層厚度與溝道的長度比值,使得性能得到了加強(由于SiO2 可以提供無與倫比的Si 鈍化作用,它的相對介電常數-只有4 -在柵極長度,柵極厚度按比例減小時,就變得太低了)。

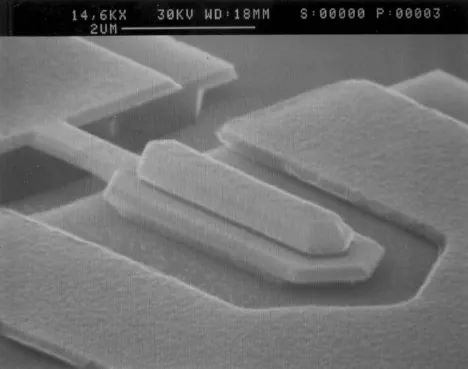

圖2、在互連之前,發射極寬度為0.6μm 的InP DHBT 的顯微照片。HBT 是采用三層臺面(Triple-Mesa)自對準工藝制作的[18]。

受益于這種擴展的頻率性能,在過去幾年,人們已經在毫米波領域對MOS 技術的潛力進行了初步的評估[23]。高集成度和低成本(對于大量芯片)是我們對硅工藝感興趣的主要原因。

III-V 器件:與CMOS的共同集成

為了同時獲得兩種技術領域的最佳優勢,異質集成工藝是一個頗有前途的解決方案。為了將III-V 晶體管(實際上是InP 晶體管)和硅基CMOS 進行相近的集成,人們已經探索了不同的途徑,特別是在DARPA 資助的COSMOS 項目中[24]。人們已經探索了若干種方法,從超級自對準(小于5μm)倒裝芯片集成到一個完全徹底的單片失配外延技術。早期的結果非常鼓舞人心,在將InP 器件集成到CMOS 圓晶片之后,InP 器件的性能劣化并不明顯,并且已經演示了一類具有大輸出擺幅和小功耗的大增益-帶寬的差分放大器(>100GHz)[25]。雖然沒有直接的聯系,但人們應當注意到,通過MOSFET技術中的高遷移率III -V 溝道層的研究而在沿著半導體國際技術路線發展藍圖道路上所取得的進展[26]。

從晶體管到電路

我們在上一節介紹了現有的用于有源器件的不同工藝的特性。這些器件是開啟100-GHz 以上頻率大門的關鍵,但這還不夠。同樣需要合適的方式將它們變為可運行的電路,這意味著傳輸線,無源器件和接地等特定領域的開發。由于這些因素,在將器件特性轉換到應用領域時,某一種工藝可能比其它的都要好。

目前,人們已可以明確不同技術在特定方面的勝出,見表3。

這個表繪制了一幅演變現狀的畫面。在接下來的討論中,將用兩種不同類型的演示電路來對畫面進行具體的說明。T.Swan,Y.Baeyens,和M.Meghelli 在文章中對特定的100-Gb/s 光波電路在該方面的進展進行了討論[53]。

用靜態分頻器作為技術的衡量基準

用于數字電路的半導體工藝通常是用靜態分頻器的性能來作為衡量基準的。由于一個靜態分頻器使用的是可以在更復雜的時序電路中找到的觸發器單元元件[36],因此這樣一個電路的性能可以作為公認的數字集成電路工藝的質量因數。相同的觸發器被用作分頻器,判斷電路,10/100-Gb/s 系統復用器的基本單元[37]。在使用類似基礎元件的不同電路中,選擇靜態分頻器的原因是因為它恰好是采用簡單的測量設備最容易進行明確評估的電路,并且它可以給出這個技術所能達到的明確的性能上限。

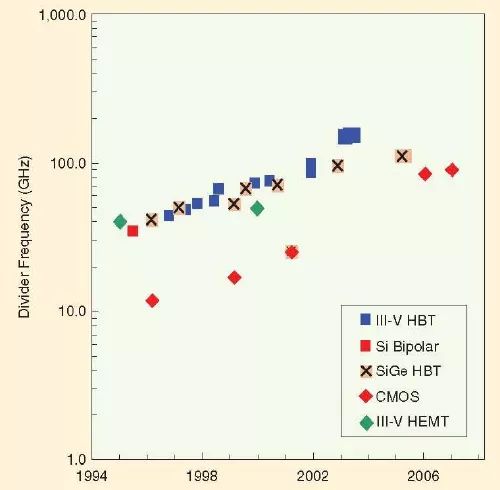

圖3 示出了從90 年代初期直到現在所報道的靜態分頻器的速度。數據顯示出在過去幾年中,即使在2000年高速光纖的市場崩潰之后,速度也是在穩定上升的。最近的進展中大部分是由DARPA 通過頻率捷變數字合成發射機技術這個計劃(TFAST)所資助的。注意,在InP HBT 技術上正持續不斷獲得最好的結果,SiGe HBT 緊隨其后[38]。HEMT 或CMOS器件技術在最高頻率方面沒有那么強的競爭力,因為在FET 為基的器件中,需要大的器件尺寸才能達到必要的跨導要求。至今為止,所發表的靜態分頻器的最好結果是采用250-nm InP HBT 技術所達到的150GHz,最近的進展已經集中到降低功耗這方面了[39]。這個性能與全速率判斷電路的性能是一致的,并且在多路復用器/多路分離器(MUX/DEMUX)電路中的性能還有很大的發展余地。

圖3、靜態頻分器的最高頻率隨著報道年代而發生的變化。所示數據僅僅了包含了當時特定技術的最好結果。

在最高工作速度下,功耗是特別重要的,此時單個門電路會有幾百毫瓦的功耗。雖然功耗隨著分頻器切換率的提高而迅速增長(例如,在87GHz時是23mW[41]),但CMOS 由于其出色的結果(輸入頻率范圍是90-100GHz[40])而加入了競爭行列。所報道的最好的功耗是采用InP HBT 技術,在150GHz 時為42mW/每個鎖存器[39]。

用振蕩器(VCO)作為技術衡量基準

壓控振蕩器(VCO)是100Gb/s 串行應答器以及下毫米波通信,高分辨率雷達和成像系統所必不可少的構建模塊。這樣的振蕩器要求將低相位噪聲,高輸出功率和好的直流-到-射頻轉換效率相結合,特別是在最高頻率下。這便轉換為許多重要的技術要求。

• 最高振蕩頻率(fmax)對于亞毫米波操作來說是很關鍵的;最高頻率基頻振蕩器是基于納米級別的InP 基HEMT。所報道的最高基頻振蕩器是已有十年歷史的213-GHz InP HEMT 振蕩器[42]。近來,采用35-nm柵極InP HEMT 技術具有Fmax 為600-GHz 的器件的fmax 的進一步改善使得基頻振蕩器可以達到346GHz[43] 。InPDHBT 最近也同樣展示了在亞毫米波頻率的基頻振蕩[44]。

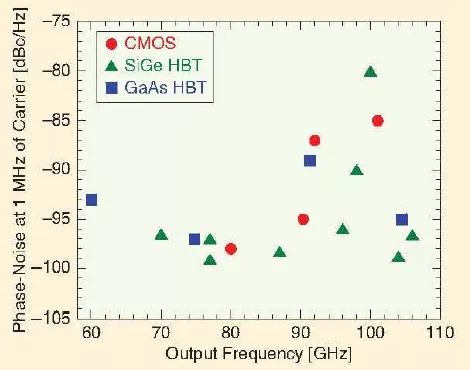

• 為了獲得振蕩器好的近載波相位噪聲性能,重要的是使用具有低閃爍噪聲的技術。雙極技術,如SiGe 或InP HBT 通常可以提供比諸如HEMT或CMOS 這類FET 更低的1/f 拐角頻率,這要歸功于表面狀態影響的減少。在觀察較大頻率偏離處的相位噪聲時(例如,距離載波1MHz-見圖4),毫米波CMOS 振蕩器所展示的相位噪聲與它們所對應的SiGe 和InP HBT 器件的相接近。這個比較并未將調諧范圍的影響考慮在內,而且還會受到曲解,即如文獻[45]中所提到的,在沒有輸出緩沖時,振蕩器毫米波頻率相位噪聲會更好一些。

圖4、所報道的采用不同技術所實施的毫米波振蕩器相位噪聲概觀(在偏離載波1-MHz 處)。

• 最后,振蕩器在最高頻率下可實現的輸出功率便成了一個重要的設計參數,特別是當器件工作在接近其fmax 時,這是因為,此時要進一步放大輸出信號會變得格外困難。為了讓輸出功率達到最大,振蕩器內部電壓的擺幅需要達到最大。大多數III-V 器件,如InP HBT 就擊穿電壓而言具有不折不扣的優勢,尤其是當其與CMOS 相比較時。這樣便可以產生所報道的較高的輸出功率。

100GHz 以上的高效率高功率源推-推振蕩器

為了在100GHz 以上達到較高的振蕩器輸出功率,設計者們更傾向于推-推振蕩器拓撲結構,在這個結構中,兩個以相反相位相耦合的振蕩器的輸出合成到一起來產生一個具有強二階諧波的輸出信號。這個拓撲結構使得可以在現有有源器件技術上實現高于fmax 的信號源,并且可以將現有高-Q 值諧振器技術的頻率范圍擴展[46]。此外,采用推-推拓撲結構,可以使用工作在基頻而不是二階諧波輸出頻率的靜態或動態分頻器來將相位鎖相環(PLL)的振蕩器鎖定,以實現頻率鎖定信號源,從而將分頻器的速度要求降低了一半。

毫米波頻率的推-推振蕩器的潛力已經得到了充分的展示。用不同的化合物半導體技術所實現的推-推振蕩器已經在文獻中有所報道:在[47]中報道了直到140GHz 的0.13μmGaAs PHEMT 振蕩器,和在[48]中所報道的可以直到278GHz 的SiGe HBT 振蕩器。即使是采用CMOS 技術也成功地實現了100GHz以上的信號源:人們已經報道了一個采用130-nmCMOS 技術的192GHz 推-推振蕩器[49]。最近,采用45-nm CMOS 技術構建了一臺工作在410GHz 的信號源[50]。然而,即使是采用推-推拓撲結構,由于硅基高速技術降低了的擊穿電壓以及納米級CMOS 需要在低偏置電壓下工作,在100GHz 以上可以觀察到CMOS 推-推振蕩器明顯降低了的輸出功率。例如,410-GHzCMOS 信號源具有20nW的輸出功率,這可能不足以用在發射機應用中或驅動接收機的混頻器中。正如在下列段落中所說明的,具有如此高功率的推-推振蕩器的理想選擇是InP 雙-異質結HBT(D-HBT)技術,它將高的fmax 和高的擊穿電壓結合在一起。

振蕩頻率在220 和355GHz 的集成推-推振蕩器是由Alcatel-Lucent/Bell- 實驗室的0.5μm 發射極InGaAs/InP HBT D-HBT 技術來實現的,具有的最大振蕩頻率為335GHz 和4V 的擊穿電壓(Vbceo)[51]。

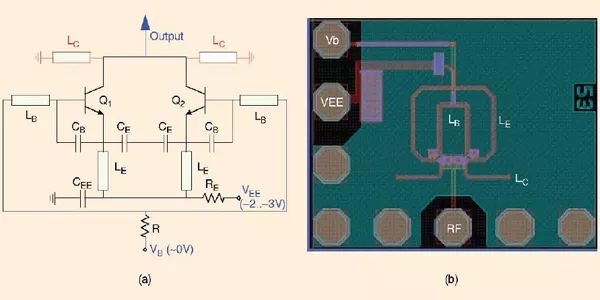

這些振蕩器是基于一種平衡Colpitts 振蕩器拓撲結構的。通過將相位相反的輸出進行合成,并且使用短路截線(short stub)通過電抗部分在二階諧波頻率上來調節振蕩器輸出阻抗使其產生一個很強的二階諧波信號[52],如圖5 所示。人們已經采用這個技術實現了不同的諧振器。圖5 展示一個287GHz 的電路布局圖。傳輸線諧振器LE,LB 和LC 是在7-μm 低-K 層間介電材料(εr=2.6)之上采用一個2-μm 厚的金板接地面通過薄膜微帶線來實現的。

圖5、一臺InP D-HBT 推-推振蕩器的(a)電路圖和(b)電路布局圖[52]。

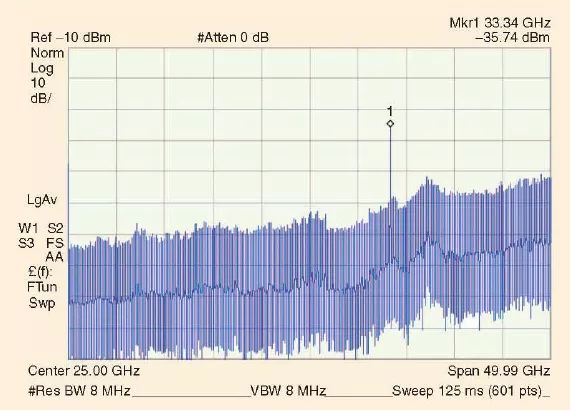

不同振蕩器的輸出信號是采用一個WR03 波導探頭來探測的,并且使用WR03 次諧波混頻器進行下變頻的。在210GHz 和235GHz 所測得的輸出功率可達1mW,直流-到-射頻的效率為2-3%。工作在280 和297GHz 的振蕩器可以獲得-5dBm 的輸出功率。圖6 展示了所實現的最高頻率振蕩器所測得的輸出頻譜。雖然輸出超過了WR03 波導(LO)在片探頭和下變頻混頻器的頻段范圍,在將振蕩器信號與321.6GHz 的有效本振頻率相混頻時,仍然會探測到很強的IF 信號。通過對探頭和混頻器損耗進行校正,損耗值估計在23dB 與30dB 之間,在355GHz 上可以獲得高于-13dBm的輸出功率。

圖6、一個工作在355GHz 的InP D-HBT 推-推VCO 的下變頻頻譜(LO=321.6GHz,上邊帶)(未對混頻器的損耗進行任何修正)。

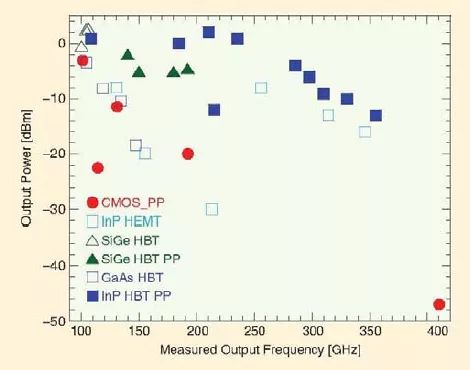

這些振蕩器的輸出功率與振蕩頻率的關系展示在圖7 中,并且將其與不同的半導體技術所制作的振蕩器進行了比較。多虧了InP D-HBT 的高擊穿電壓,以及可以將輸出功率改善5dB 的二階諧波調諧技術,截止目前為止,InP D-HBT 推-推振蕩器可以在該頻段范圍內具有比所報道的其它晶體管信號源更高的輸出功率和效率。

圖7、所報道的采用不同技術所實施的振蕩器的輸出功率和工作頻率的概觀。采用基頻和推-推振蕩器的結果分別用空心和實心符號來表示。

結論

若干種半導體材料和技術都適合用來解決100GHz 和100-Gb/s 的應用問題。這些技術有時候會相互競爭,正如我們所預期的,這是一個新的應用領域,人們仍然在對這些技術各自的優點和缺點進行著討論。本文旨在說明隨著頻率性能的不斷提高,這些演進技術的多樣性和其潛在的影響。盡管長期以來,器件性能的改善僅僅依賴于光刻技術進步所允許的尺寸的減小,然而異質結構和應力工程技術現在已成為強有力的手段,通過它們可以增強速度和功率性能,使之達到能夠打開100-GHz 和100-Gb/s 應用領域之門的水平。

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底