一、理論知識

發送端 AB間的電壓差

+2 ~ +6v 邏輯1

-2 ~ -6v 邏輯0;

接收端 AB間的電壓差

大于 +200mv 邏輯1

小于 -200mv 邏輯0

定義邏輯1為B>A的狀態

定義邏輯0為A>B的狀態

AB之間的電壓差不小于200mv

(其實一直沒搞懂AB差分線是有參考GND線嗎,希望有大佬解答)

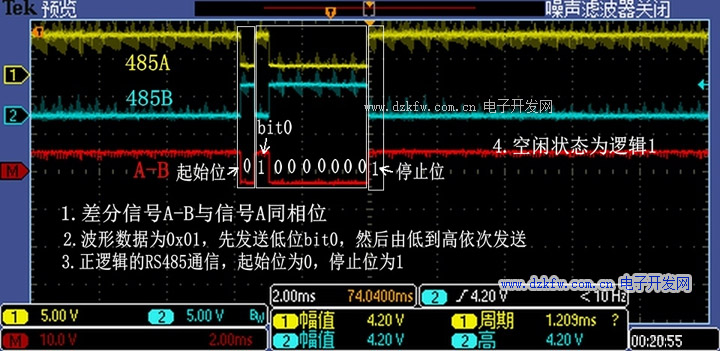

二、波形分析

三、電路理解

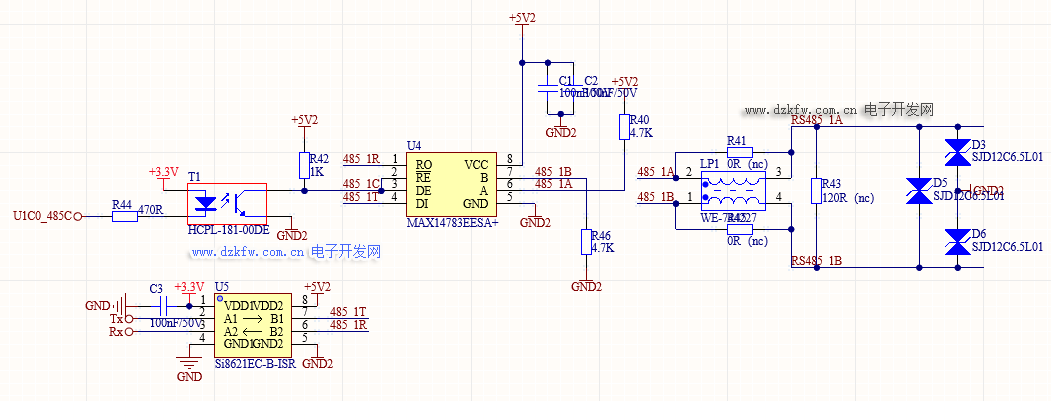

1 帶隔離的基本485電路,芯片選用MAX14783。2 自動切換電路

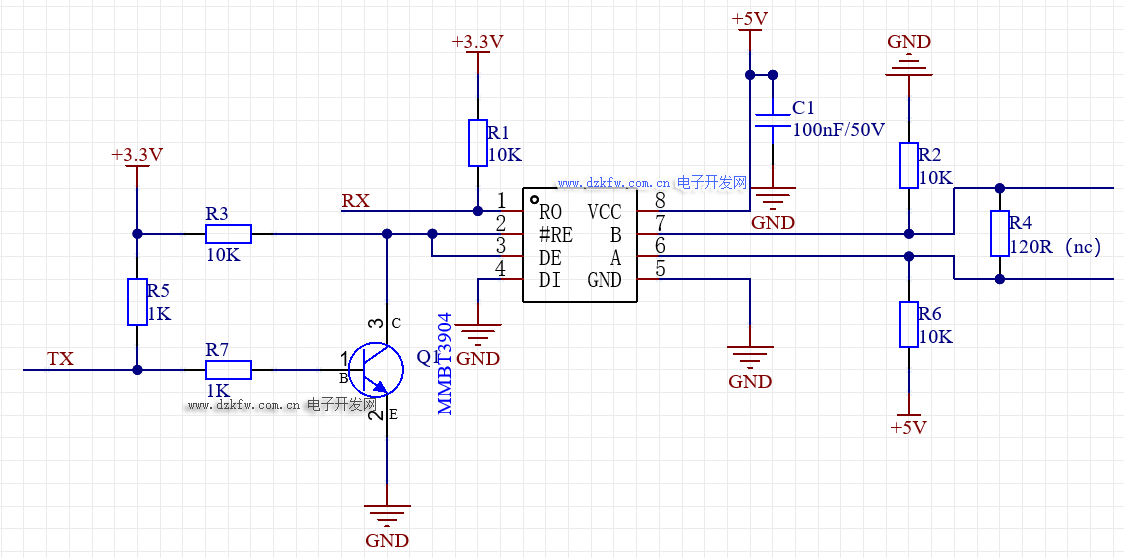

TX\RX需要上拉電阻

接收:默認沒有數據時,TX為高電平,三極管導通,RE為低電平使能,RO收數據有效,MAX為接收狀態

發送:發送1時,TX為高電平,三極管導通,DE為低電平,此時收發器處于接收狀態,驅動器就變成了高組態,也就是發送端和AB斷開了,此時AB之間的電壓就取決于AB的上下拉電阻,A為高電平,B為低電平,也就是邏輯1.

發送0時,TX為低電平,三極管截止,DE為高電平,驅動器使能,此時正好DI接地,也就是低電平,驅動器也就會驅動輸出B為1,A為0,也就是所謂的邏輯0.。

理解自收發的作用,關鍵要理解RE和DE的作用,尤其當DE為0時,驅動器與AB之間就是高阻態,也就是斷開狀態,而且AB都要有上下拉電阻,然后就有了邏輯0/1之間的切換。

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底