三分頻電路介紹

電路一

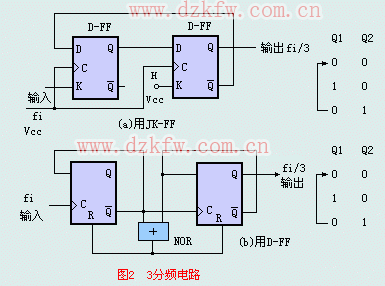

圖2是3分頻電路,用JK-FF實(shí)現(xiàn)3分頻很方便,不需要附加任何邏輯電路就能實(shí)現(xiàn)同步計(jì)數(shù)分頻。但用D-FF實(shí)現(xiàn)3分頻時(shí),必須附加譯碼反饋電路,如圖2所示的譯碼復(fù)位電路,強(qiáng)制計(jì)數(shù)狀態(tài)返回到初始全零狀態(tài),就是用NOR門(mén)電路把Q2,Q1=“11B”的狀態(tài)譯碼產(chǎn)生“H”電平復(fù)位脈沖,強(qiáng)迫FF1和FF2同時(shí)瞬間(在下一時(shí)鐘輸入Fi的脈沖到來(lái)之前)復(fù)零,于是Q2,Q1=“11B”狀態(tài)僅瞬間作為“毛刺”存在而不影響分頻的周期,這種“毛刺”僅在Q1中存在,實(shí)用中可能會(huì)造成錯(cuò)誤,應(yīng)當(dāng)附加時(shí)鐘同步電路或阻容低通濾波電路來(lái)濾除,或者僅使用Q2作為輸出。D-FF的3分頻,還可以用AND門(mén)對(duì)Q2,Q1譯碼來(lái)實(shí)現(xiàn)返回復(fù)零。

電路二

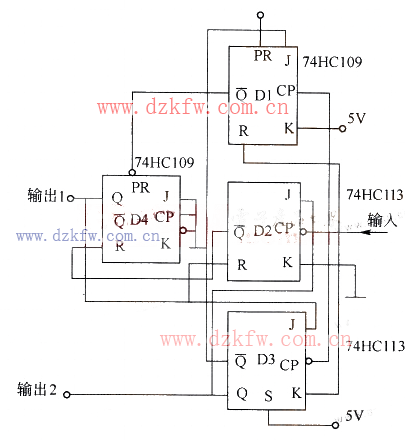

如圖所示是由雙上升沿J - K觸發(fā)器74HC109與雙下降沿J - K觸發(fā)器74HC113組成的三分頻電路,利用該電路可以得到對(duì)稱(chēng)的分頻輸出。

三分頻電路,在電路圖中,在一般的利用常規(guī)計(jì)數(shù)器對(duì)數(shù)字脈沖進(jìn)行奇數(shù)分頻時(shí),即使輸入是對(duì)稱(chēng)信號(hào), 輸出也得不到占空比為50%的分頻輸出,其原因是內(nèi)部觸發(fā)器采用的是統(tǒng)一的上升沿(或下降沿)進(jìn)行觸發(fā)。在本例中,利用- K觸發(fā)器D1、D2分別由不同的時(shí)鐘沿觸發(fā)這一特性,將DI、D2與D4結(jié)合起來(lái)可以得到占空比為50%的分頻輸出。再與D3組合,就可以構(gòu)成對(duì)稱(chēng)輸出的三分頻電路。

電路三

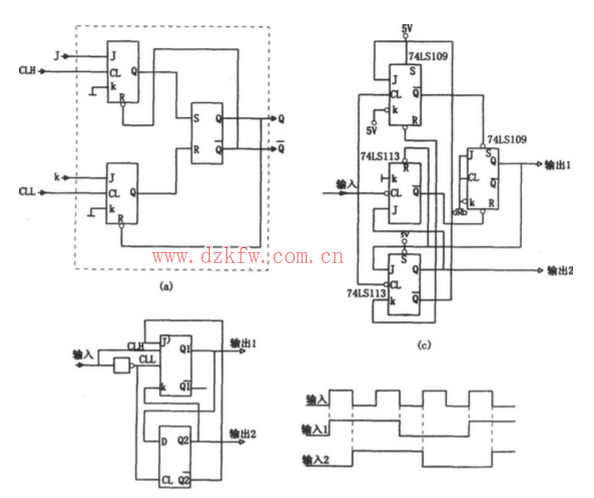

如圖所示為對(duì)稱(chēng)輸出的=三分頻電路。在~般的利用常規(guī)計(jì)數(shù)器對(duì)數(shù)字脈沖進(jìn)行奇數(shù)分頻時(shí),即使輸入是對(duì)稱(chēng)信號(hào),輸出也得不到占空比為50%的分頻輸山,其原因是內(nèi)部觸發(fā)器采用的是統(tǒng)一的上升沿(或下降沿)進(jìn)行觸發(fā)。為了解決此問(wèn)題,可以利用一個(gè)J和K分別由不同時(shí)鐘沿觸發(fā)的JK觸發(fā)器,如圖(a)所示。該電路內(nèi)部由兩個(gè)JK觸發(fā)器和“個(gè)RS觸發(fā)器構(gòu)成,其等效J端由CLH觸發(fā),而等效K端由CLL端觸發(fā),其余功能與~般的JK觸發(fā)器相同。將圖(a)作為個(gè)單元與一個(gè)常規(guī)的D觸發(fā)器組合,并在時(shí)鐘端加上反相器,可以構(gòu)成對(duì)稱(chēng)輸出的三分頻電路,如圖(b)所示。圖(C)是一個(gè) 實(shí)際應(yīng)用電路。圖中因?yàn)椴捎昧讼陆笛赜|發(fā)的74LS113,所以省去了它與74LS109時(shí)鐘端之間的反相器。電路74L S109和74LS113的-半構(gòu)成圖(a)同樣功能的電路。而74LS113的另- *半 相當(dāng)于圖(b)的D觸發(fā)器

返回頂部

返回頂部 刷新頁(yè)面

刷新頁(yè)面 下到頁(yè)底

下到頁(yè)底