鎖相的意義是相位同步的自動控制,能夠完成兩個電信號相位同步的自動控制閉環系統叫做鎖相環,簡稱PLL。它廣泛應用于廣播通信、頻率合成、自動控制及時鐘同步等技術領域。

一個典型的鎖相環(PLL)系統,是由鑒相器(PD),壓控蕩器(VCO)和低通濾波器(LPF)三個基本電路組成,如圖1,

圖1

一.鑒相器(PD)

構成鑒相器的電路形式很多,這里僅介紹實驗中用到的兩種鑒相器。

1.異或門鑒相器 異或門的邏輯真值表示于表1,圖2是邏輯符號圖。

|

| ||||||||||||||||||

|

圖2 |

表1 | ||||||||||||||||||

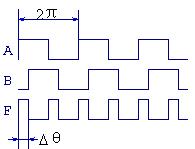

從表1可知,如果輸入端A和B分別送入占空比為50%的信號波形, 則當兩者存在相位差Dθ時,輸出端F的波形的占空比與Δθ有關,見圖3。將F輸出波形通過積分器平滑,則積分器輸出波形的平均值,它同樣與Δθ有關,這樣,我們就可以利用異或門來進行相位到電壓的轉換,構成相位檢出電路。于是經積分器積分后的平均值(直流分量)為:

U = Vdd * Δ θ/π (1)

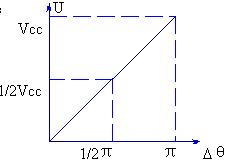

不同的Δθ,有不同的直流分量Vd。Δθ與V的關系可用圖4來描述。從圖中可知,兩者呈簡單線形關系:

Ud = Kd *Δθ (2)

Kd 為鑒相靈敏度

圖3 圖4

2.邊沿觸發鑒相器 前已述及,異或門相位比較器在使用時要求兩個作比較的信號必須是占空比為50%的波形,這就給應用帶來了一些不便。而邊沿觸發鑒相器是通過比較兩輸入信號的上跳邊沿(或下跳邊沿)來對信號進行鑒相,對輸入信號的占空比不作要求。

二.壓控振蕩器(VCO)

壓控振蕩器是振蕩頻率ω0受控制電壓UF(t)控制的振蕩器,即是一種電壓——頻率變換器。VCO的特性可以用瞬時頻率ω0(t)與控制電壓UF(t)之間的關系曲線來表示。未加控制電壓時(但不能認為就是控制直流電壓為0,因控制端電壓應是直流電壓和控制電壓的疊加),VCO的振蕩頻率,稱為自由振蕩頻率ωom,或中心頻率,在VCO線性控制范圍內,其瞬時角頻率可表示為:

ωo(t)= ωom + K0 UF(t)

式中,K0——VCO控制特性曲線的斜率,常稱為VCO的控制靈敏度,或稱壓控靈敏度。

三.環路濾波器

這里僅討論無源比例積分濾波器如圖5。其傳遞函數為:

式中:τ1 = R1 C

τ2 = R2 C

圖5

四.鎖相環的相位模型及傳輸函數

圖6

圖6為鎖相環的相位模型。要注意一點,鎖相環是一個相位反饋系統,在環路中流通的是相位,而不是電壓。因此研究鎖相環的相位模型就可得環路的完整性能。

由圖6可知:

(1)當A點斷開環路時,鎖相環的開環相位傳輸函數為

KL(S)=

(2)環路閉合時的相位傳輸函數為

H(S)

(3)環路閉合時的相位誤差傳輸函數為

He(S)=

當環路濾波器選用無源比例積分濾波器時,經推導可得:

H(S)=

式中, ,τ1 = R1 C ,τ2 = R2 C

,τ1 = R1 C ,τ2 = R2 C

2x

x= , K = Kd Ko

, K = Kd Ko

同樣可得:

He(S)=

ωn稱為系統的固有頻率或自然角頻率;

x 稱為系統的阻尼系數。

要注意的是上面討論中的ω指的是輸入信號相位的變化角頻率,而不是輸入信號本身的角頻率。如輸入信號是調頻信號,則ω指的是調制信號的角頻率而不是載波的角頻率。

五.鎖相環的同步與捕捉

鎖相環的輸出頻率(或VCO的頻率)ωo能跟蹤輸入頻率ωi的工作狀態,稱為同步狀態,在同步狀態下,始終有ωo = ωi。在鎖相環保持同步的條件下,輸入頻率ωi的最大變化范圍,稱為同步帶寬,用DωH 表示。超出此范圍,環路則失鎖。

失鎖時,ωo≠ωi,如果從兩個方向設法改變ωi,使ωi向ωo靠攏,進而使Δωo =(ωi-ωo)↓,當Δωo小到某一數值時,環路則從失鎖進入鎖定狀態。這個使PLL經過頻率牽引最終導致入鎖的頻率范圍稱為捕捉帶Δωp。同步帶ΔωH,捕捉帶Δωp 和VCO 中心頻率ωo的 關系如圖7。

圖7

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底