1.在適當的LR中保存下一條指令的地址,當異常入口來自:

ARM狀態,那么ARM7TDMI將當前指令地址加4或加8復制(取決于異常的類型)到LR中;

為Thumb狀態,那么ARM7TDMI將當前指令地址加4或加8 (取決于異常的類型)復制到LR中;異常處理器程序不必確定狀態。

2.將CPSR復制到適當的SPSR中;

3. 將CPSR模式位強制設置為與異常類型相對應的值;

4.強制PC從相關的異常向量處取指。

ARM7TDMI內核在中斷異常時置位中斷禁止標志,這樣可以防止不受控制的異常嵌套。

注:異常總是在ARM狀態中進行處理。當處理器處于Thumb狀態時發生了異常,在異常向量地址裝入PC時,會自動切換到ARM狀態。

關于“退出異常”:當異常結束時,異常處理程序必須:

1.將LR中的值減去偏移量后存入PC,偏移量根據異常的類型而有所不同;

2.將SPSR的值復制回CPSR;

3.清零在入口置位的中斷禁止標志。

注:恢復CPSR的動作會將T、F和I位自動恢復為異常發生前的值。

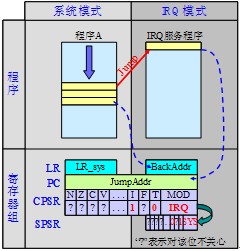

下面利用,圖示來演示“進入異常”過程:

1. 程序在系統模式下運行用戶程序,假定當前處理器狀態為Thumb狀態、允許IRQ中斷;

2. 用戶程序運行時發生IRQ中斷,硬件完成以下動作:

(1)將CPSR寄存器內容存入IRQ模式的SPSR寄存器

(2)置位I位(禁止IRQ中斷)

(3)清零T位(進入ARM狀態)

(4)設置MOD位,切換處理器模式至IRQ模式

(5)將下一條指令的地址存入IRQ模式的LR寄存器

(6)將跳轉地址存入PC,實現跳轉

圖示“退出異常”過程:

在異常處理結束后,異常處理程序完成以下動作:

(1)將SPSR寄存器的值復制回CPSR寄存器;

(2)將LR寄存的值減去一個常量后復制到PC寄存器,跳轉到被中斷的用戶程序。

在異常處理結束后,異常處理程序完成以下動作:

(1)將SPSR寄存器的值復制回CPSR寄存器;

(2)將LR寄存的值減去一個常量后復制到PC寄存器,跳轉到被中斷的用戶程序。

不管異常入口是來自ARM狀態還是Thumb狀態,FIQ處理程序都會通過執行下面的指令從中斷返回: SUBS PC,R14_fiq,#4

在一個特權模式中,可以通過置位CPSR中的F位來禁止FIQ異常。

關于“中斷請求”:中斷請求(IRQ)異常是一個由nIRQ輸入端的低電平所產生的正常中斷(在 具體的芯片中,nIRQ由片內外設拉低,nIRQ是內核的一個信號,對用戶不可見)。IRQ的優先級 低于FIQ。對于FIQ序列它是被屏蔽的。任何時候在一個特權模式下,都可通過置位CPSR中的I 位來禁止IRQ。

不管異常入口是來自ARM狀態還是Thumb狀態,FIQ處理程序都會通過執行下面的指令從中斷返回: SUBS PC,R14_fiq,#4

關于“中止”:中止發生在對存儲器的訪問不能完成時,中止包含兩種類型:

(1)預取中止:發生在指令預取過程中

(2)數據中止:發生在對數據訪問時

中止——預取指中止:當發生預取中止時,ARM7TDMI內核將預取的指令標記為無效,但在指 令到達流水線的執行階段時才進入異常。如果指令在流水線中因為發生分支而沒有被執行,中止將不會發生。在處理中止的原因之后,不管處于哪種處理器操作狀態,處理程序都會執行下面的指令恢復PC和CPSR并重試被中止的指令: SUBS PC,R14_abt,#4

中止——數據中止:當發生數據中止后,根據產生數據中止的指令類型作出不同的處理:

(1)數據轉移指令(LDR、STR)回寫到被修改的基址寄存器。中止處理程序必須注意這一點;

(2)交換指令(SWP)中止好像沒有被執行過一樣(中止必須發生在SWP指令進行讀訪問時);

(3)塊數據轉移指令(LDM,STM)完成。 當回寫被設置時,基址寄存器被更新。在指示出現中止后,ARM7TDMI內核防止所有寄存器被覆蓋。這意味著ARM7TDMI內核總是會保護被中止的LDM指令中的R15(總是最后一個被轉移的寄存器)。

在修復產生中止的原因后,不管處于哪種處理器操作狀態,處理程序都必須執行下面的返回指令 : SUBS PC,R14_abt,#8

關于“軟件中斷指令”:使用軟件中斷(SWI)指令可以進入管理模式,通常用于請求一個特定的管理函數。SWI處理程序通過執行下面的指令返回: MOVS PC,R14_svc

這個動作恢復了PC和CPSR并返回到SWI之后的指令。SWI處理程序讀取操作碼以提取SWI函數編號。

關于“未定義的指令”:當ARM7TDMI處理器遇到一條自己和系統內任何協處理器都無法處理的指令時,ARM7TDMI內核執行未定義指令陷阱。軟件可使用這一機制通過模擬未定義的協處理器指令來擴展ARM指令集。

注:ARM7TDMI處理器完全遵循ARM結構v4T,可以捕獲所有分類未被定義的指令位格式。在模擬處理了失敗的指令后,陷阱程序執行下面的指令:MOVS PC,R14_svc

這個動作恢復了PC和CPSR并返回到未定義指令之后的指令。

關于“異常優先級”:當多個異常同時發生時,一個固定的優先級系統決定它們被處理的順序:

注意:(1)未定義的指令和SWI異常互斥。因為同一條指令不能既是未定義的,又能產生有效的軟件中斷;

(2)當FIQ使能,并且FIQ和數據中止異常同時發生時,ARM7TDMI內核首先進入數據中止處理程序,然后立即跳轉到FIQ向量。在FIQ處理結束后返回到數據中止處理程序。數據中止的優先級必須高于FIQ以確保數據轉移錯誤不會被漏過。

(2)當FIQ使能,并且FIQ和數據中止異常同時發生時,ARM7TDMI內核首先進入數據中止處理程序,然后立即跳轉到FIQ向量。在FIQ處理結束后返回到數據中止處理程序。數據中止的優先級必須高于FIQ以確保數據轉移錯誤不會被漏過。

Tags:ARM處理器,異常模式

責任編輯:admin相關文章列表

沒有相關文章 [ 查看全部 ] 網友評論

推薦文章

最新推薦

熱門文章

返回頂部

返回頂部 刷新頁面

刷新頁面 下到頁底

下到頁底